Supporting Information

## Control of Multilevel Resistance in Vanadium Dioxide by Electric Field using Hybrid Dielectrics

Kaleem Abbas<sup>1</sup>, Jaeseok Hwang<sup>1</sup>, Garam Bae<sup>1</sup>, Hongsoo Choi<sup>2</sup> and Dae Joon Kang<sup>1,\*</sup>

<sup>1</sup>Department of Physics and Energy Science, Sungkyunkwan University, 2066, Seobu-ro, Jangan-gu, Suwon 16419, Gyeoggi-do, Republic of Korea

\*djkang@skku.edu

<sup>2</sup>Department of Robotics Engineering, Daegu Gyeongbuk Institute of Science and Technology (DGIST), 711-873, Daegu, Republic of Korea

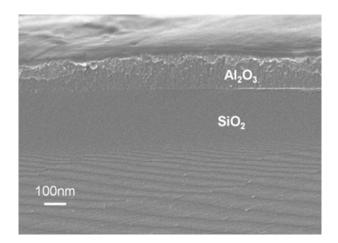

Figure S1, Cross-sectional SEM image of SiO2 and Al2O3 hybrid dielectric layer. SEM image shows that Al2O3 of 200 nm thickness was deposited on SiO2 layer of 300 nm. Then VO2 film was doposited and FET-VO2 device was fabricated on hybrid dielectric of 500 nm thickness. Cross-sectional image shows a good interface quality between the two dielectric layers.

| No | Device structure                                   | VO2 thickness<br>~(nm) | Dielectric layer                                 | Dielectric thickness<br>~(nm) | leakage    |

|----|----------------------------------------------------|------------------------|--------------------------------------------------|-------------------------------|------------|

| 1  | VO₂/SiO₂/Si <sup>+</sup>                           | 100                    | SiO <sub>2</sub>                                 | 100                           | High       |

| 2  | VO <sub>2</sub> /SiO <sub>2</sub> /Si <sup>+</sup> | 100                    | SiO <sub>2</sub>                                 | 200                           | High       |

| 3  | VO <sub>2</sub> /SiO <sub>2</sub> /Si <sup>+</sup> | 100                    | SiO <sub>2</sub>                                 | 300                           | small      |

| 4  | $VO_2/AI_2O_3/SiO_2/S^+$                           | 100                    | Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> | 200/300                       | Very small |

Table S1; Summary of VO2 devices fabricated of different dielectric layer thickness.

It should be noted that the thickness of the VO<sub>2</sub> film was kept constant (~100nm) for all devices. Instead, we vary the thickness of the dielectric layer as shown in the Table S1. The main purpose of varying the thickness of the dielectric layer was to choose the optimized layer thickness in order to minimize the leakage current while observing a clear gate effect on VO<sub>2</sub> devices as evident in Figure 5b. We found that both 100 nm and 200 nm thick SiO<sub>2</sub> dielectric layers showed a very high leakage current. Further, we showed that the SiO<sub>2</sub> layer of 300 nm thickness and  $Al_2O_3/SiO_2$  hybrid dielectric layer of 200/300 nm thickness were thick enough to show pronounced gate effects on VO<sub>2</sub> devices. We believe that further increase in the thickness would not change its electrical transport characteristics much especially in the case of hybrid dielectric layer.