## Supporting Information

to the manuscript

# Enabling Energy Efficiency and Polarity-Control in Germanium Nanowire Transistors by Individually Gated Nano-Junctions

Jens Trommer, André Heinzig, Uwe Mühle, Markus Löffler, Annett Winzer, Paul M. Jordan, Jürgen Beister, Tim Baldauf, Marion Geidel, Barbara Adolphi, Ehrenfried Zschech, Thomas Mikolajick and Walter M. Weber

### **Table of Content**

| 1. Pulsed Measurement Setup                                                                  | p.2 |

|----------------------------------------------------------------------------------------------|-----|

| 2. XPS Data on planar Al <sub>2</sub> O <sub>3</sub> /GeO <sub>x</sub> /Ge Reference samples | p.3 |

| 3. Review of Reconfigurable Circuit Design Possibilities                                     | p.4 |

| References Supporting Information                                                            | p.6 |

#### 1. Pulsed Measurement Setup

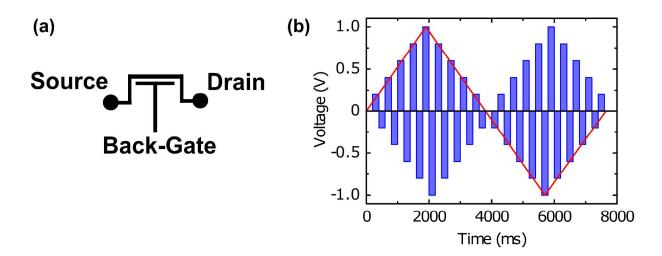

In order to eliminate hysteresis and noise caused by interface defects and border traps a pulsed measurement scheme as proposed by Mattmann *et al.* was applied.<sup>1</sup> Thereto, each individual measurement pulse is followed by a detrapping pulse of the same magnitude in the opposite direction. Figure S1 shows a schematic comparison of the applied voltage scheme at the controlling gate for continuous (red) and pulsed (blue) measurements. In contrast to continuous sweep, in the pulsed regime the gate bias is always switched to its negated value after each pulse. The voltages applied between source and drain contacts are kept constant. It can be seen in Figure 1(c) in the main-paper (in this case, the controlling gate is the back-gate) that this methodology effectively reduced the hysteresis and thus gives access to the intrinsic device properties.

Figure S1: (a) Schematic device layout corresponding to the back-gated characteristics shown in Figure 1. (b) Applied pulse gate sweep method (blue) as compared to the continuous sweep (red) at the gate contact in order to reduce the influence of hysteresis and noise. All measurements are carried out in a common source scheme. Measurement data is shown in Figure 1 within the main paper.

#### 2. XPS results on planar Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge Reference samples

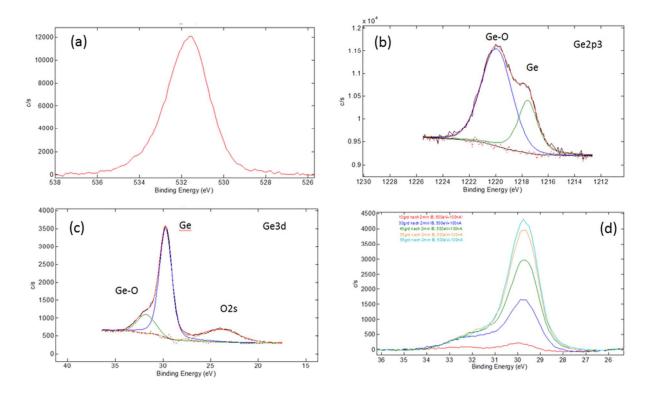

The in-situ formation of a  $GeO_x$  interface passivation layer during the ALD process was analyzed on planar reference samples using XPS techniques. Thereto, a silicon wafer with a 100 nm thick metal-organic CVD epitaxial grown germanium layer (GeOnSi p-doped with 10<sup>18</sup> atoms/cm<sup>3</sup>) were etched in 5% HF solution for 5 min and immediately covered with 24 cycles of Al<sub>2</sub>O<sub>3</sub> employing the same process as for the nanowire devices. The XPS analysis was carried out using the  $Al_{K\alpha}$  line with energy of 1486.6 eV as X-ray source. Prior to measurement the surface was cleaned for 2 min by Ar sputtering with 500 eV in order to remove surface contamination. As the O1s binding energies of Al<sub>2</sub>O<sub>3</sub> and GeO<sub>2</sub> overlap (compare Table StI and Figure S2) the stoichiometry of the interface layer was analyzed based on the Ge3d and Ge2p3 peak positions and compared with database values for GeO<sub>2</sub> and GeO. For both binding energies a distinct oxide peak is present next to the peak assigned with pure Ge-Ge bonds. This is a clear hint on the formation of the intended germanium oxide interface. However, as both positions are located between the literature values of GeO<sub>2</sub> and GeO they could not be unambiguously assigned to one of the oxidation states. Consequently, it can be inferred that the in-situ interface is not pure stoichiometric but rather a mixture of GeO<sub>2</sub> and GeO. Angle resolved X-ray photoelectron spectroscopy (ARXPS) as described in detail by Paynter<sup>2</sup> and Kozlowska<sup>3</sup> was applied in order to estimate the thickness of this interfacial layer to be less than 1 nm. This is in accordance with the cross sectional TEM images of a fully process device shown in Figure 2(c) in the main paper where a formation of a sub-nanometer amorphous interlayer below the Al<sub>2</sub>O<sub>3</sub> shell is indicated.

| EMISSION LINE | Material                       | Nominal Binding energy (eV) | MEASURED ENERGY VALUES<br>(EV) |

|---------------|--------------------------------|-----------------------------|--------------------------------|

| 01s —         | GeO <sub>2</sub>               | 531.6 532.3                 | 531.8                          |

|               | Al <sub>2</sub> O <sub>3</sub> | 531.0 532.0                 | 531.8                          |

| Ge3d          | Ge                             | 28.6 29.6                   | 29.7                           |

|               | GeO                            | 30.9                        | 31.8                           |

|               | GeO <sub>2</sub>               | 32.5 33.1                   |                                |

| Ge2p3         | Ge                             | 1217.2 1217.6               | 1217.6                         |

|               | GeO                            | 1218                        | 1219.9                         |

|               | GeO <sub>2</sub>               | 1220.2 1220.6               |                                |

TABLE STI

COMPARISON OF XPS PEAK POSITIONS MEASURED ON A PLANAR AL2O3/GE STACK WITH DATABASE VALUES

Figure S2: XPS spectra taken from a planar reference sample of the  $Al_2O_3/GeO_x/Ge$  stack. (a) Oxide peak, (b) Ge2p3 peak, (c) Ge3d peak (d), evolution of Ge3d peak during ARXPS used for interface thickness determination.

#### 3. Review of Reconfigurable Circuit Design Possibilities

The idea of reconfigurable electronics is to provide a flexible platform, where the end user is able to respond to recent technological developments and adapt the digital circuits through updates without having to directly change the underlying hardware. Reconfigurable electronics thus provide an increased functionality and higher flexibility in the design of circuits and systems as compared to classical CMOS technology. Basically, there are two different methodologies to realize reconfigurable circuits: The redirection of data paths to predefined areas with specific functionalities on the one hand, and the reprogramming of single devices and gates on the other hand. The first approach, known as *coarse-grained* systems, has been already studied since 1984 in the form of Field Programmable Gate Arrays (FPGA), where typically either a multiplexertree (MUX-tree) or static random access memory (SRAM) based look-up table (LUTs) is facilitated to provide multiple functions in a user-accessible fashion. In contrast the research in the area of *fine-grained* reconfigurability has just started to evolve in the last few years, mainly due to the earlier lack of an efficient physical concept providing a dynamic reconfiguration on the device level. This changed with the discovery of polarity-control in doping-free nanoscale Schottky barrier transistors.<sup>4,5</sup> The first designs of fine-grain reconfigurable circuits employing polarity-controllable devices were described in 2006 by Ian O'Conner et al.,<sup>6,7</sup> who demonstrated the possibility to produce user-configurable dynamic logic blocks out of double-gated carbon nanotube field effect transistors (CNTFETs). The proposed reconfigurable logic blocks had the

possibility to provide up to 8 functions with as little as 9 transistors. However, one drawback of those gates was, that they were not operating completely complementary for every possible combination of input and select signals and thus suffered from output swing degradation. Also, being dynamic logic gates, the need for having two independent clocking signals in order to precharge the individual branches limited their applicability in FPGAs. Nonetheless, the cell designs have been improved over the last years by introducing transmission gates.<sup>8</sup> Another versatile approach is resulting out of the transformation rules given by DeMorgan's law. Exploiting the feature of polarity-control, an arbitrary logic gate can be switched to its logical complement simply by reversing all programming voltages and inverting the supply potentials.<sup>9,10</sup> A simple example is given by a six transistor cell that provides not-and (NAND), not-or (NOR) and majority (MAJ) function, which compares to a logic gate with at least 10 transistors in standard CMOS technology. The concept can be extended to exclusive-or (XOR), exclusive-not-or (XNOR) and and-or-invert (AOI) gates.<sup>10</sup> Importantly, the cells always operate in a complementary mode and deliver a full swing output. Different to CMOS, complemental functions exhibit the same delay, which origins from the electrical symmetric underlying device technology.<sup>11</sup> First FPGA architectures have been proposed employing ultrafine-grain reconfigurable logic cells based on such Schottky barrier nanowire field effect transistors.<sup>8,12</sup> In a different approach the increased expressive capability of the polarity-controllable devices is utilized internally in order to yield a higher functional density as compared to classical technologies.<sup>13</sup> As one example Michele DeMarchi et al.<sup>14</sup> showed that dual-gated silicon nanowire field effect transistors intrinsically support the XOR function. First measured demonstrator circuits have shown that one and the same cell built from those devices can be operated either as XOR or as NAND gate, depending on the wiring conditions.<sup>15</sup> Dense regular arrays of such cells can consecutively be hard-programmed by the connecting metal layers to the desired functionality. Employing these so called uncommitted logic-gate patters it is possible to design logic circuits in a more compact memory-array-like style, increasing the lavout regularity.<sup>16</sup> Further optimization can take place when transistors with three or more independent gates are applied.<sup>12,17</sup> These so-called multiple-independent-gate field effect transistors (MIGFETs) can be used to merge several transistors in series into a single device. As a result more compact circuit designs can be achieved despite the larger individual footprint of the devices themselves. We have recently calculated that an 8-bit full adder circuit can be built from roughly half the number of transistors.<sup>18</sup> Indeed a high number of junctions and isolations are saved, reducing the overall size, even if the individual device is larger. First assessments have indicated that those fine-grain reconfigurable circuits have benefits in terms of performance and energy consumption, while also needing less area than a comparable CMOS FinFET or fullydepleted silicon-on-insulator (FDSOI) technology.<sup>12,16,18–20</sup>

#### **References Supporting Information**

- Mattmann, M.; Bechstein, D.; Roman, C.; Chikkadi, K.; Hierold, C. Reduction of Gate Hysteresis above Ambient Temperature *via* Ambipolar Pulsed Gate Sweeps in Carbon Nanotube Field Effect Transistors for Sensor Applications. *Appl. Phys. Lett.* 2010, *97*, 153103.

- (2) Paynter, R. W. Angle-Resolved X-Ray Photoelectron Spectroscopy Studies of the Evolution of Plasma-Treated Surfaces with Time. *Surf. Interface Anal.* **1999**, *27*, 103–113.

- (3) Kozłowska, M.; Reiche, R.; Oswald, S.; Vinzelberg, H.; Hübner, R.; Wetzig, K. Quantitative ARXPS Investigation of Systems with Ultrathin Aluminium Oxide Layers. *Surf. Interface Anal.* **2004**, *36*, 1600–1608.

- (4) Lin, Y.-M.; Appenzeller, J.; Knoch, J.; Avouris, P. High-Performance Carbon Nanotube Field-Effect Transistor with Tunable Polarities. *IEEE Trans. Nanotechnol.* **2005**, *4*, 481–489.

- (5) Weber, W. M.; Geelhaar, L.; Lamagna, L.; Fanciulli, M.; Kreupl, F.; Unger, E.; Riechert, H.; Scarpa, G.; Lugli, P. Tuning the Polarity of Si-Nanowire Transistors Without the Use of Doping. In 8th IEEE Conference on Nanotechnology, 2008. NANO '08; 2008; pp. 580–581.

- (6) Liu, J.; O'Connor, I.; Navarro, D.; Gaffiot, F. Design of a Novel CNTFET-Based Reconfigurable Logic Gate. In *IEEE Computer Society Annual Symposium on VLSI, 2007. ISVLSI '07*; 2007; pp. 285–290.

- (7) O'Connor, I.; Junchen, L.; Gaffiot, F.; Pregaldiny, F.; Lallement, C.; Maneux, C.; Goguet, J.; Fregonese, S.; Zimmer, T.; Anghel, L.; Dang T.-T.; Leveugle R. CNTFET Modeling and Reconfigurable Logic-Circuit Design. *IEEE Trans. Circuits Syst. Regul. Pap.* 2007, 54, 2365–2379.

- (8) Gaillardon, P.-E.; Tang, X.; Kim, G.; De Micheli, G. A Novel FPGA Architecture Based on Ultra-Fine Grain Reconfigurable Logic Cells. *IEEE Trans. Very Large Scale Integr. Syst.* 2014.

- (9) Trommer, J.; Heinzig, A.; Slesazeck, S.; Mikolajick, T.; Weber, W. M. Elementary Aspects for Circuit Implementation of Reconfigurable Nanowire Transistors. *IEEE Electron Device Lett.* **2014**, *35*, 141–143.

- (10) Trommer, J.; Heinzig, A.; Baldauf, T.; Slesazeck, S.; Mikolajick, T.; Weber, W. M. Functionality-Enhanced Logic Gate Design Enabled by Symmetrical Reconfigurable Silicon Nanowire Transistors. *IEEE Trans. Nanotechnol.* **2015**, *14*, 689–698.

- (11) Heinzig, A.; Mikolajick, T.; Trommer, J.; Grimm, D.; Weber, W. M. Dually Active Silicon Nanowire Transistors and Circuits with Equal Electron and Hole Transport. *Nano Lett.* 2013, 13, 4176–4181.

- (12) Trommer, J.; Heinzig, A.; Baldauf, T.; Mikolajick, T.; Weber, W. M.; Raitza, M.; Völp, M. Reconfigurable Nanowire Transistors with Multiple Independent Gates for Efficient and Programmable Combinational Circuits. In 2016 Design, Automation Test in Europe Conference Exhibition (DATE); 2016; pp. 169–174.

- (13) Amaru, L.; Gaillardon, P.-E.; De Micheli, G. Efficient Arithmetic Logic Gates Using Double-Gate Silicon Nanowire FETs. In *New Circuits and Systems Conference (NEWCAS)*, 2013 IEEE 11th International; 2013; pp. 1–4.

- (14) De Marchi, M.; Sacchetto, D.; Frache, S.; Zhang, J.; Gaillardon, P.; Leblebici, Y.; De Micheli, G. Polarity Control in Double-Gate, Gate-All-around Vertically Stacked Silicon Nanowire FETs. In *Electron Devices Meeting (IEDM), 2012 IEEE International*; 2012; pp. 8.4.1–8.4.4.

- (15) De Marchi, M.; Zhang, J.; Frache, S.; Sacchetto, D.; Gaillardon, P.-E.; Leblebici, Y.; De Micheli, G. Configurable Logic Gates Using Polarity-Controlled Silicon Nanowire Gate-All-Around FETs. *IEEE Electron Device Lett.* 2014, *35*, 880–882.

- (16) Gaillardon, P.-E.; Amaru, L.; Zhang, J.; De Micheli, G. Advanced System on a Chip Design Based on Controllable-Polarity FETs. In *Proceedings of the Conference on Design, Automation & Test in Europe*; DATE '14; European Design and Automation Association: 3001 Leuven, Belgium, Belgium, 2014; pp. 235:1–235:6.

- (17) Zhang, J.; Tang, X.; Gaillardon, P.-E.; De Micheli, G. Configurable Circuits Featuring Dual-Threshold-Voltage Design With Three-Independent-Gate Silicon Nanowire FETs. *IEEE Trans. Circuits Syst. Regul. Pap.* **2014**, *61*, 2851–2861.

- (18) Raitza, M.; Trommer, J.; Völp, M.; Walter, D.; Mikolajick, T.; Kumar, A.; Walter M. Weber. Exploiting Transistor-Level Reconfiguration to Optimize Combinational Circuits. *Proc. Des. Autom. Test Eur.* **2017**.

- (19) Gaillardon, P.-E.; Amarù, L. G.; Bobba, S.; De Marchi, M.; Sacchetto, D.; Leblebici, Y.; De Micheli, G. Vertically-Stacked Double-Gate Nanowire FETs with Controllable Polarity: From Devices to Regular ASICs. In *Proceedings of the Conference on Design, Automation and Test in Europe*; DATE '13; EDA Consortium: San Jose, CA, USA, 2013; pp. 625–630.

- (20) Gaillardon, P.-E.; Amarù, L. G.; Bobba, S.; Marchi, M. D.; Sacchetto, D.; Micheli, G. D. Nanowire Systems: Technology and Design. *Philos. Trans. R. Soc. Math. Phys. Eng. Sci.* 2014, 372, 20130102.