## **Supporting Information**

## Low-Voltage and High Performance Multilayer MoS<sub>2</sub> Field-effect Transistors with

## **Graphene Electrodes**

Arun Kumar Singh<sup>1,2\*</sup>, Chanyong Hwang<sup>3</sup> and Jonghwa Eom<sup>1</sup>

<sup>1</sup>Department of Physics and Graphene Research Institute, Sejong University, Seoul 143-747, Korea.

<sup>2</sup>Department of Physics, Motilal Nehru National Institute of Technology, Allahabad-211004, India.

<sup>3</sup>Center for Nanometrology, Korea Research Institute of Standards and Science, Daejeon 305-

340, Korea.

\*Corresponding Author E.mail: arunsingh.itbhu@gmail.com

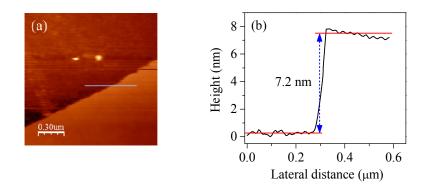

**Figure S1.** Atomic force microscopic image of a) ML MoS<sub>2</sub> and b) corresponding height profile for ML MoS<sub>2</sub> films. The thickness is about 7.2 nm, indicating 10 MoS<sub>2</sub> layers.

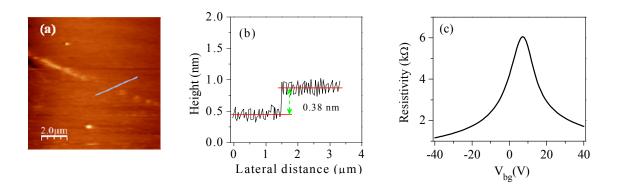

Figure S2. Atomic force microscopic image of a) CVD-grown SLG and b) corresponding height profile. The thickness is about 0.38 nm, indicating SLG. c) Resistivity as a function of back gate voltage ( $V_{bg}$ ) for CVD grown SLG

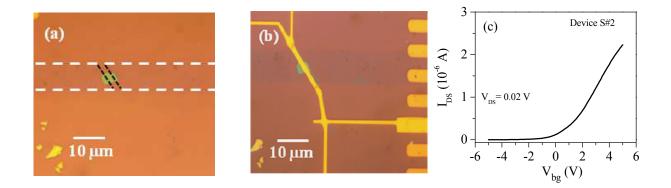

**Figure S3.** a) Optical image of the fabricated device (device S#2), CVD-grown SLG as the source–drain electrode, and ML MoS<sub>2</sub> as the channel material. b) Optical image of the fabricated top-gated ML MoS<sub>2</sub> transistor. The ML MoS<sub>2</sub> is covered with 15-nm-thick film of ALD-deposited Al<sub>2</sub>O<sub>3</sub> acting as a gate dielectric and Cr/Au with 5/80 nm for the top-gated electrodes. c) Plot of  $I_{DS}-V_{bg}$  of the ML MoS<sub>2</sub> transistor after Al<sub>2</sub>O<sub>3</sub> deposition at  $V_{DS} = 0.02$  V. Mobility of device S#2 is estimated found to be 466 cm<sup>2</sup>/Vs.