# **Supplementary Information**

# Role of remote interfacial phonon (RIP) scattering in heat transport across

## graphene/SiO<sub>2</sub> interfaces

Yee Kan Koh<sup>1</sup>, Austin S. Lyons<sup>2</sup>, Myung-Ho Bae,<sup>2,3</sup> Bin Huang,<sup>1</sup> Vincent E. Dorgan,<sup>2</sup> David G. Cahill<sup>4</sup>, and Eric Pop<sup>2,5</sup>

<sup>1</sup>Department of Mechanical Engineering, and Centre for Advanced 2D Materials, National University of Singapore, Singapore

<sup>2</sup>Department of Electrical & Computer Engineering, Micro and Nanotechnology Lab, University of Illinois, Urbana, Illinois 61801, USA

<sup>3</sup>Korea Research Institute of Standards and Science, Daejeon 34113, Republic of Korea

<sup>4</sup>Department of Materials Science and Engineering, and Frederick Seitz Materials Research Laboratory, University of Illinois, Urbana, Illinois 61801, USA

<sup>5</sup>Department of Electrical Engineering and Precourt Institute for Energy, Stanford University,

Stanford, CA 94305, USA

#### **S1.** Fabrication process

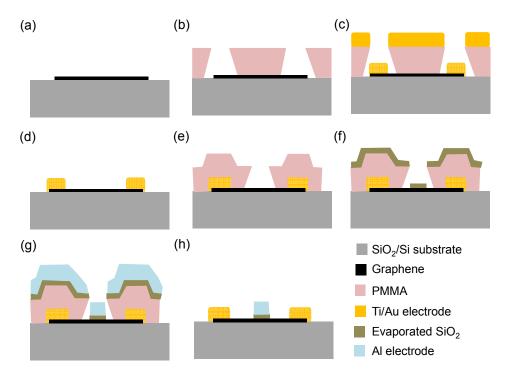

Dual-gated graphene field-effect transistors were prepared by nano-fabrication processes as shown in Supplementary Fig. 1.

- (a) Graphene flakes were mechanically exfoliated on a SiO<sub>2</sub>/Si substrate and a graphene flake is located by an optical microscope.

- (b) A PMMA (Polymethyl methacrylate) layer was coated on the substrate at 6000 rpm and baked at 200 °C for 2 minutes. Two regions of the selected graphene were exposed to the air after e-beam lithography and development processes.

- (c) Ti (10 nm) and Au (40 nm) were successively deposited by a thermal e-beam evaporation.

- (d) A lift-off process with acetone left a graphene with source and drain electrodes.

- (e) With the same recipe of (b) for the PMMA coating and e-beam lithography process, a region between the source and drain was developed.

- (f) SiO<sub>2</sub> (~24 nm) was thermally evaporated by an e-beam evaporator at ~8 ×  $10^{-7}$ Torr.

- (g) After transferring the substrate to another e-beam evaporator, a Al (90 nm) were deposited.

- (h) After a lift-off process in acetone, a top-gated graphene field-effect transistor was completed.

**Supplementary Fig. S1** Schematic of fabrication process of a graphene dual-gated field-effect transistor.

### S2. Sample images and Raman spectra

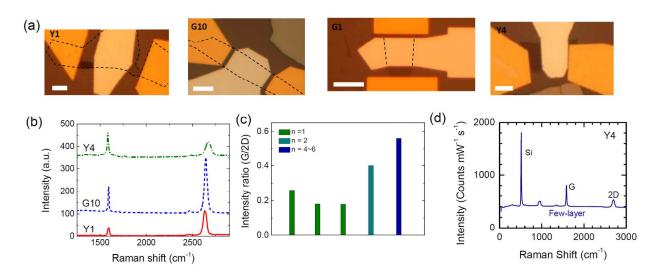

**Supplementary Fig. S2** (a) Optical microscope images of samples, Y1, G10, G1 and Y4. Scale bar are 10  $\mu$ m. (b) Raman spectra of Y1, G10 and Y4. (c) Intensity ratio of G and 2D peak (G/2D) of G4, Y1, G10, G1 and Y4. In Ref. [S1], it has been shown that the G/2D intensity ratio gives the number of graphene layer (*n*): 0.2~0.3, 0.35~0.41, 0.45~0.55, 0.53~0.71 and 0.6~0.8 for *n* = 1, 2, 3, 4 and 6, respectively. Following this report, we assigned *n* as shown in the figure. (d) Raman spectrum of Y4. For the sample Y4, the intensity ratio of G and Si peaks, 0.49 was additionally considered and we confirmed *n* = 6 for Y4 [2].

### **S3.** Electrical characterization

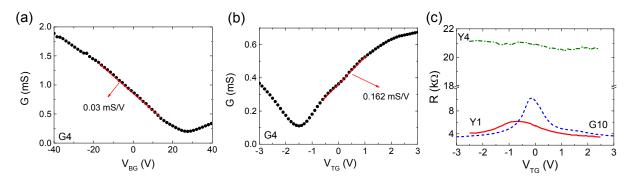

**Supplementary Fig. S3** Electrical conductance as a function of (a) back-gate voltage  $(G-V_{BG})$  and (b) top-gate voltage  $(G-V_{TG})$  of G4. Here  $G-V_{BG}$  was obtained before defining the top gate. We estimated a low-field mobility from the transfer curve based on a relation of  $\mu = \frac{L}{W} \frac{1}{C_{ox}} \frac{dG}{dV_G}$ , where  $C_{ox}$  is the gate capacitance per unit area and  $V_G$  is the gate voltage. The back-gate channel length is  $L_{BG} = 33.7 \,\mu\text{m}$ , top-gate channel length,  $L_{TG} = 25 \,\mu\text{m}$  and channel width,  $W = 14 \,\mu\text{m}$ . With slopes of linear regions in the transfer curves of (a) and (b), indicated by red solid lines, we get mobility of  $\mu_{BG} = 1820 \,\text{cm}^2 \text{V}^{-1} \text{S}^{-1}$  and  $\mu_{TG} = 1950 \,\text{cm}^2 \text{V}^{-1} \text{S}^{-1}$ , respectively. Here, we used the dielectric constant for both of back- and top-gate SiO<sub>2</sub> layers as 3.9. Since the both mobility for the back- and top-gate effect is the similar value with the same dielectric constant, we confirmed that the thermally evaporated 24 nm thick top-SiO<sub>2</sub> shows the dielectric constant as ~3.9 as a usual value. (c) Resistance vs. top-gate voltage (*R*-*V*<sub>TG</sub>) curves for Y1, G10 and Y4.

#### S4. Sensitivity plots

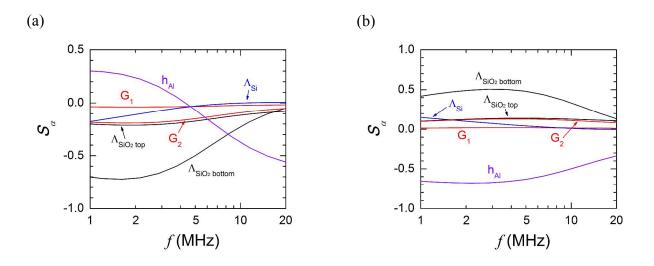

**Supplementary Fig. S4** (a) Sensitivity of V<sub>out</sub> signals and (b) V<sub>in</sub>/V<sub>out</sub> signals to various parameters used in the thermal model, as a function of modulation frequency *f*. We used the structure of sample G1 for the calculation, which is a multilayered structure consisting of 84 nm Al / 25 nm SiO<sub>2</sub> / exfoliated graphene / 90 nm SiO<sub>2</sub> / Si substrate. The parameters are thermal conductance of Al/SiO<sub>2</sub> interface *G*<sub>1</sub>, thermal conductance of SiO<sub>2</sub>/G/SiO<sub>2</sub> interface *G*<sub>2</sub>, thermal conductivity of Si substrate  $\Lambda_{Si}$ , thermal conductivity of top SiO<sub>2</sub> layer  $\Lambda_{SiO2 \text{ top}}$ , thermal conductivity of bottom SiO<sub>2</sub> layer  $\Lambda_{SiO2 \text{ bottom}}$  and thickness of Al  $\Lambda_{Al}$ . We fix the delay time at -40 ps and 100 ps for (a) and (b) respectively and assume a laser spot  $1/e^2$  radii of 4 µm. As illustrated in the figures, we choose to use V<sub>out</sub> and *f* ≈ 10 MHz in our VMTR measurements, to achieve the highest sensitivity to *G*<sub>2</sub> and lowest sensitivity to other parameters.

#### S5. Comparison of raw data of TDTR and VMTR

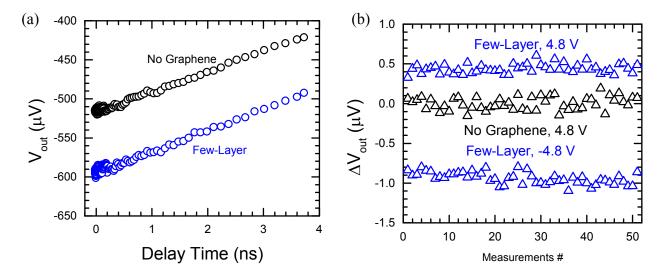

**Supplementary Fig. S5** (a) Out-of-phase components of TDTR measurements ( $V_{out}$ ) on the fewlayer graphene sample and a region without graphene on a sample, as labeled. In these measurements, we used a modulation frequency of 10 MHz, a total laser power of ~62 mW and laser spot sizes of ~4 µm. The noise, usually on the order of 2% of the signals (~10 µV), originates from the noise in laser intensity, the variation of phase in the rf lock-in amplifier, etc. From measurements to measurements, the precision of TDTR measurements is on the order of 1% (~5 µV), usually limited by phrase drift in the rf lock-in amplifier. (b) VMTR measurements on the same sample as in (a), using the same laser power and laser spot size as in (a). The "on"-state gate voltages that we applied are as labeled. By averaging 40-100 VMTR measurements as in the figure, we are able to reduce the uncertainty of VMTR measurements to ~0.012 µV, more than 100 times better than the uncertainty of TDTR measurements.

#### **References for Supplementary information**

- [1] D. Graf et al., Nano Letters 7, 238 (2007)

- [2] Y.K. Koh, M.-H. Bae, D.G. Cahill, E. Pop, ACS Nano 5, 269 (2011).