## Aligned Epitaxial SnO<sub>2</sub> Nanowires on Sapphire:

## Growth and Device Applications – Supporting

## Information

Xiaoli Wang,<sup>†,‡</sup> Noppadol Aroonyadet,<sup>†,‡</sup> Yuzheng Zhang,<sup>§</sup> Matthew Mecklenburg,<sup>§</sup> Xin Fang,<sup>§</sup> Haitian Chen,<sup>†</sup> Edward Goo,<sup>§</sup> Chongwu Zhou<sup>†,\*</sup>

<sup>†</sup>Department of Electrical Engineering, <sup>§</sup>Department of Chemical Engineering and Material Science, and <sup>||</sup>Center for Electron Microscopy and Microanalysis, University of Southern California, Los Angeles, CA 90089

**Materials** A-plane, M-plane, and R-plane sapphire wafers with 2-inch diameter were purchased from University Wafers with the primary flats oriented in C plane, C plane, and A plane, respectively. Sn powder precursor was purchased from Alfa Aesar, and purities of both 99.99% and 99.995% were used. Au catalysts were deposited by evaporating a metal source purchased from Plasmaterials. The Ar used as the carrier gas during nanowire synthesis was purchased as ultra high purity Ar (99.999%) from Gilmore Liquid and Gas Company. NO<sub>2</sub> gas used for chemical sensing was purchased as 1030 ppm NO<sub>2</sub> balanced with Ar from Airgas.

Aligned SnO<sub>2</sub> nanowire synthesis The sapphire substrates were cleaned by sonication in acetone, followed by rinsing in acetone, isopropyl alcohol, and distilled water, then dried in a gas stream. Ambient annealing of M-plane sapphire substrates was done at 1400°C<sup>1</sup> in a 1500°C maximum tube furnace from Lindberg/Blue M with a ramping rate of 23°C/min. An 1100°C one-inch tube furnace from Lindberg/Blue M was used to anneal the A-plane sapphire in air.<sup>2</sup> Annealing time is 1.5 hours. After annealing, stripes of 5 µm by 5-30 µm, and about 100 µm apart were perpendicularly patterned to the primary flat of each substrate so that the catalyst stripes are perpendicular to the direction of aligned SnO2 nanowire growth. An Au catalyst thickness of 3 nm to 6 nm was confirmed using an atomic force microscope (AFM). Before nanowire synthesis, substrates with Au catalyst were placed into the one-inch furnace to complete a thermal de-wetting step at 800°C for 15 minutes in ambient air. The synthesis of aligned SnO<sub>2</sub> nanowires was carried out in a horizontal quartz tube in the one-inch furnace. The Sn powder precursor was placed upstream in a quartz boat. The different planes of sapphire substrates with the de-wetted Au catalysts were placed in the same quartz boat downstream of the precursor. The boat was positioned in the center of the one-inch quartz furnace tube and then heated to 900°C for one hour at a ramping rate of approximately 45 degrees per minute. Argon was used as the carrier gas, and a mechanical pump with a pumping rate of 4 m<sup>3</sup>/h was used to sustain the pressure inside the furnace at around 200 Torr for growing aligned SnO<sub>2</sub> nanowires.

Field effect transistor (FET) fabrication Sapphire substrates containing aligned SnO<sub>2</sub> nanowires were sonicated in isopropyl alcohol (IPA) to remove the small amounts of free-standing un-aligned SnO<sub>2</sub> nanowires on the surface. Following substrate cleaning, source and drain electrodes were patterned on the substrates using bi-layered photoresist and standard photolithography. The metals Ti and Au were then deposited into the electrode patterns through electron beam evaporation at a thickness of 5 nm and 75 nm respectively. Afterwards, an uniform layer of 40 nm aluminum oxide was deposited as gate dielectric through atomic layer deposition (ALD). Next, photolithography was used again to pattern the gate electrode, which was deposited using the same process as source and drain deposition. Lastly, buffered oxide etch (BOE) was used to remove aluminum oxide over the source and drain in order to form contacts to the electrodes.

Scanning electron microscopy (SEM) images of SnO<sub>2</sub> nanowires and devices were taken using a Hitachi field-emission scanning electron microscope at a voltage of 1 kV. Surface scans of sapphire was made using tapping AFM in tapping mode. Current measurements for FET, photoconduction, and chemical sensing experiments were done using semiconductor analyzer Agilent 4156B.

**Figure S1.** Histograms of nanowire assembly parameters of aligned SnO<sub>2</sub> nanowires on annealed A-plane, annealed M-plane, and R-plane sapphire. (a - c) aligned SnO<sub>2</sub> nanowire density on annealed A- plane (a), annealed M-plane, (b) and R-plane sapphire substrates (c) from 20 samples for each plane. (d-e) SnO<sub>2</sub> nanowire alignment defect density on annealed A- plane (d), annealed M-plane (e), and R-plane sapphire substrates (f) from 20 samples for each plane. (g-i) nanowire misalignment angles of 100 nanowires from 20 samples on annealed A- plane (g), annealed M-plane (h) and R-plane sapphire substrates (i)

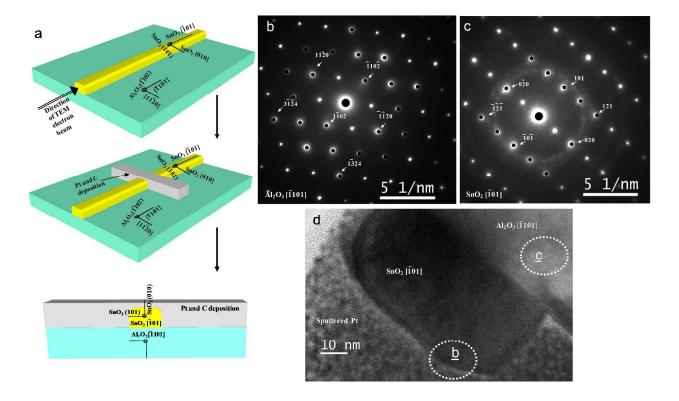

Figure S2. Transmission electron microscopy (TEM) imaging of aligned SnO<sub>2</sub> nanowire on R-plane sapphire substrate. (a) Diagram of cross-sectional sample preparation by FIB lift-out technique, from the as-grown sample to protective platinum and carbon deposition, and to finished cross-sectional TEM sample. Direction of the electron beam is parallel to the nanowire growth direction as indicated by the double arrow. (b) Bright spots are electron diffraction pattern of sapphire taken from the cross-sectional sample. Black dots are simulated diffraction pattern of sapphire looking into the [T101] lattice vector direction. (c) Bright spots are electron diffraction pattern of SnO<sub>2</sub> taken from the cross-sectional sample. Black dots are simulated diffraction pattern of SnO<sub>2</sub> looking into the [T01] lattice vector direction. The faint rings are diffraction from the protective Pt layer. (d) TEM image showing the location on the cross-sectional sample from where the SnO<sub>2</sub> electron beam diffraction patterns in (b) and (c) are taken. Area enclosed by the dashed circles with underscored b and c correspond to image (b) and (c), respectively.

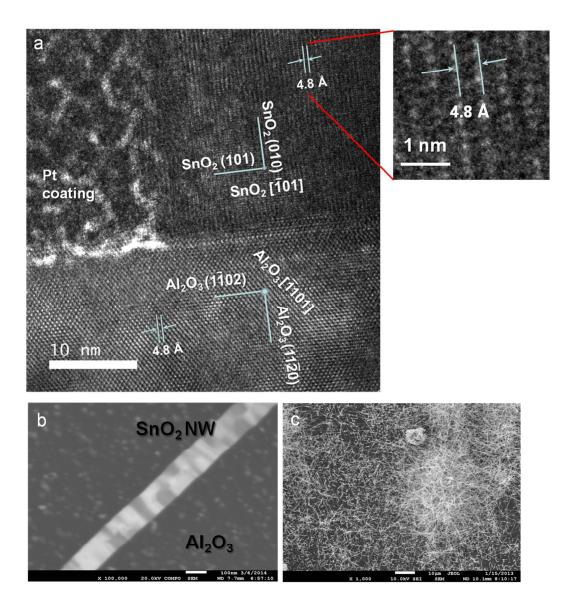

**Figure S3.** (a) High-resolution TEM image of the cross section of an aligned SnO<sub>2</sub> nanowire on R-plane sapphire substrate. (b) High-resolution SEM image of an aligned SnO<sub>2</sub> nanowire on R-plane sapphire. (c) SEM image of SnO<sub>2</sub> nanowires grown on R-plane sapphire with the synthesis pressure set to atmospheric pressure. Dense, un-aligned nanowire forest can be seen with such synthesis condition.

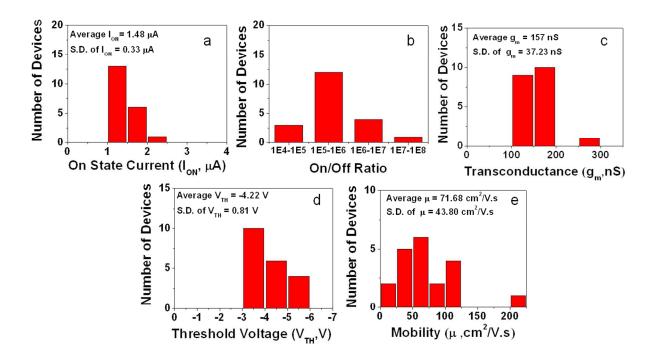

**Figure S4.** Histograms of device performance from 20 aligned  $SnO_2$  nanowire transistors. (a) On state drain current ( $I_D$ ) at  $V_D = 200$  mV,  $V_G = 10$  V. (b) On/Off ratio of  $I_D$ . (c) Transconductance ( $g_m$ ), (d) Threshold voltage ( $V_{TH}$ ). (e) Mobility ( $\mu$ ).

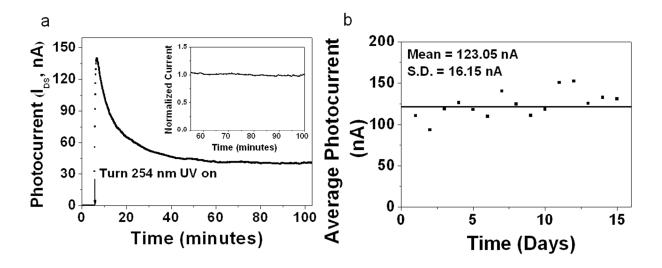

**Figure S5.** (a) Stability test of real-time response from UV 254 nm illumination on aligned  $SnO_2$  nanowire detector with  $V_{DS} = 500$  mV. Photoconduction decreased and reached steady state after

60 minutes (b) Long term stability test of photoconduction. Each data point is an average photoconduction response over 200 s after 254 nm UV illumination measured from the same sensor used in Figure 4.

## **REFERENCES**

- 1. Tsivion, D.; Schvartzman, M.; Popovitz-Biro, R.; Joselevich, E. ACS nano 2012, 6, (7), 6433-45.

- 2. Ryu, K.; Badmaev, A.; Wang, C.; Lin, A.; Patil, N.; Gomez, L.; Kumar, A.; Mitra, S.; Wong, H. S. P.; Zhou, C. W. *Nano Letters* **2009**, *9*, (1), 189-197.