## Supporting Information for "Scaling and graphical transport-map analysis of ambipolar Schottky-barrier thin-film transistors based on a parallel array of Si-nanowires"

Dae-Young Jeon,<sup>1,2</sup> Sebastian Pregl,<sup>1,2,3</sup> So Jeong Park,<sup>1,2</sup> Larysa Baraban,<sup>3</sup> Gianaurelio Cuniberti,<sup>3</sup> Thomas Mikolajick,<sup>1,4</sup> and Walter M. Weber<sup>1,\*</sup>

<sup>1</sup>Namlab gGmbH, Nöthnitzer Strasse 64, 01187 Dresden, Germany

- <sup>2</sup>Center for Advancing Electronics Dresden (CfAED), TU Dresden, 01062 Dresden, Germany

- <sup>3</sup>Institute for Materials Science and Max Bergmann Center of Biomaterials, TU Dresden, 01062 Dresden, Germany

<sup>4</sup>Chair for Nanoelectronic Materials, TU Dresden, Dresden, Germany

\*Corresponding author: walter.weber@namlab.com

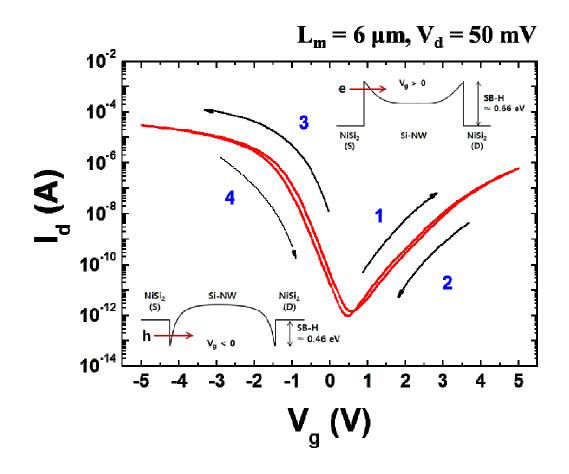

**Figure S1.** Transfer curve of the ambipolar SB-TFTs showing insignificant hysteresis effects. The hysteresis effects were also mostly vanished after annealing process in N<sub>2</sub> atmosphere at 300 °C. The numbers in the plot denote a sweep direction of V<sub>g</sub>  $(1 \rightarrow 2 \rightarrow 3 \rightarrow 4)$  and the illustrations with the inset describe the injection probability of hole or electron strongly affected by a bias condition of V<sub>g</sub>.

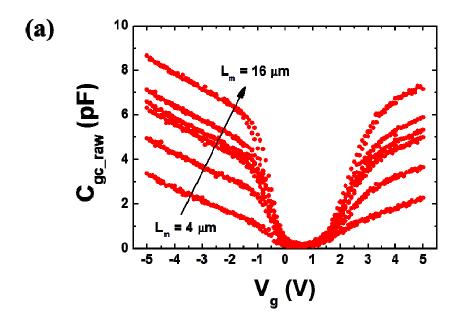

In this device for the extraction of the  $C_{gc_offset}$ , the whole area of channel is covered by  $NiSi_2(L_m = 3 \ \mu m)$ .

**Figure S2.** (a) The raw data of  $C_{gc}$  vs  $V_g$  as varying  $L_m$ . The capacitance isn't saturated even at high  $|V_g|$  due to the gate dependent off-set capacitance ( $C_{gc_offset}$ ) stemming from the particular structure of the device. (b) Optical microscope (OM) image of an ambipolar SB-TFTs, where the whole channel (the dotted white square) could be fully silicided with NiSi<sub>2</sub> and corresponding I<sub>d</sub> and  $C_{gc}$  as a function of  $V_g$ . Constant I<sub>d</sub> against  $V_g$  was observed in the inset, since I<sub>d</sub> current mostly flows through a shortest path of NiSi<sub>2</sub> in the channel. Whereas, the gate dependent  $C_{gc}$  was interestingly obtained with the same device. Si-NW in parallel could exist on the whole area of substrate. This allows that the partially silicided Si-NW in the dotted black square can cause the  $C_{gc_offset}$ , even though it hardly contributes to I<sub>d</sub>.

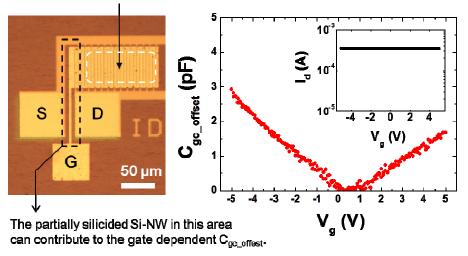

**Figures S3.** Schematic illustrating I-V map of thermionic emission (TE) dominant regime and possible band-diagram for  $I_h$  or  $I_e$  transport according to the sign of  $V_d$  bias. For  $V_d > 0$  in the TE regime,  $I_h$  and  $I_e$  can be given as, individually: <sup>1,2</sup>

$$I_e \approx A^* T^2 \times \exp^{\left(\frac{-\varphi_{B_e}}{kT/q}\right)} \times \exp^{\left(\frac{V_g - V_s - V_c}{kT/q}\right)}$$

(S1)

$$I_h \approx B^* T^2 \times \exp^{\left(\frac{-\varphi_{B_h}}{kT/q}\right)} \times \exp^{\left(\frac{V_d - V_g + V_c}{kT/q}\right)}$$

(S2)

With assumption of  $I_h = I_e$  on the border line of transition in the I-V map, a linear function of  $V_d$  vs  $V_g$  can be obtain by:

$$V_{d} = 2V_{g} + (\varphi_{Bh} - \varphi_{Be}) - 2V_{c} + V_{s} + \frac{kT}{q} \ln\left(\frac{A^{*}}{B^{*}}\right)$$

(S3)

Finally, one can get a simple equation as followings, since  $V_s = 0$  and  $kT/q \times ln(A^*/B^*)$  can be neglected at room temperature:

$$V_d \approx 2V_g + (\varphi_{Bh} - \varphi_{Be}) - 2V_c \quad (S4)$$

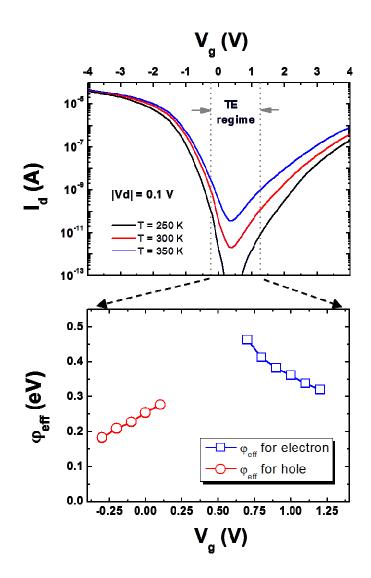

**Figure S4.** Temperature dependence of  $I_d$  vs.  $V_g$  (upper) and the effective barrier height  $\varphi_{eff}$  values extracted by  $\ln(I_d/T^2) \approx -q/kT \times \varphi_{eff}(V)$  in the TE regime (lower),  $L_m = 6 \ \mu m$ . The  $\varphi_{eff}$  is still modulated by even  $V_g$  slightly beyond flat-band voltage within the TE regime where a very small amount of tunneling current is expected, due to the image force induced lowering of the effective barrier height.<sup>1</sup>

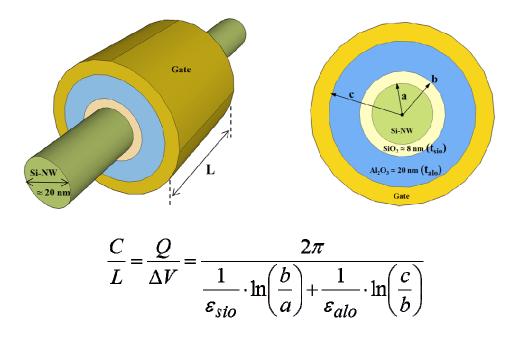

- a = radius of Si-Nanowire

- $b = a + t_{sio}$  and  $c = b + t_{alo}$

- $\varepsilon_{sio}$  and  $\varepsilon_{alo}$  are permittivity of SiO<sub>2</sub> and  $\Lambda l_2O_3$ , respectively.

**Figure S5**. Illustration of a Si-NW transistor with a perfect surrounded gate. The equation denotes capacitance per unit gate length with two dielectric materials.<sup>3,4</sup> One can calculate a capacitance per unit area of nanowire surface ( $C_{ox calcul.}$ ) as:

$$C_{ox\_calcul.} = \frac{C}{A} = \frac{C}{2a\pi \times L} = \frac{1}{a \times \left(\frac{1}{\varepsilon_{sio}} \times \ln\left(\frac{b}{a}\right) + \frac{1}{\varepsilon_{alo}} \times \ln\left(\frac{c}{b}\right)\right)}$$

(S5)

Then, the number of Si-NWs connected to source or drain was estimated as  $\approx 1.6 \times 10^3$  with  $C_{ox\_calcul.} = C_{ox\_meas.} = S/(2\pi a \times N)$ , where A, S and N represent surface area of a single nanowire, slope of  $C_{gc}$  vs.  $L_m$  in the figure 3(b) and the number of Si-NWs, respectively. The value is comparable to that ( $\approx 1.0 \times 10^3$ ) from a statistical analysis using SEM, with considering variation of nanowire diameters and assumption regarding gate geometry.

## REFERENCES

- (1) Sze, S. M.; Ng, K. K., Physics of semiconductor devices. John Wiley & Sons: 2006.

- (2) Beister, J.; Wachowiak, A.; Heinzig, A.; Trommer, J.; Mikolajick, T.; Weber, W. M. physica status solidi (c) 2014, 11, (11-12), 1611-1617.

- (3) Khanal, D.; Wu, J. Nano letters 2007, 7, (9), 2778-2783.

- (4) Xiong, W. W., Multigate MOSFET technology. In FinFETs and Other Multi-Gate Transistors, Springer: 2008; pp 49-111.