## **Supporting Information**

## Solid Electrolyte Interphase Layer Formation during Lithiation of Single Crystal Silicon Electrodes with a Protective Aluminum Oxide Coating

Arne Ronneburg<sup>1</sup>, Luca Silvi<sup>1</sup>, Joshaniel Cooper<sup>2</sup>, Karsten Harbauer<sup>3</sup>, Matthias Ballauff<sup>1,4</sup>, Sebastian Risse<sup>1\*</sup>

1: Helmholtz-Zentrum Berlin, Department for Electrochemical Energy Storage, Hahn-Meitner Platz 1, 14109, Berlin, Germany; 2: ISIS, Harwell Science and Innovation Campus, STFC, Oxon OX11 0QH, United Kingdom; 3: Helmholtz-Zentrum Berlin, Institute for Solar Fuels, Hahn-Meitner Platz 1, 14109, Berlin, Germany; 4: I Freie Universität Berlin, nstitute for Chemistry and Biochemistry, Takustraße 3, 14195 Berlin, Germany

\*corresponding author: sebastian.risse@helmholtz-berlin.de

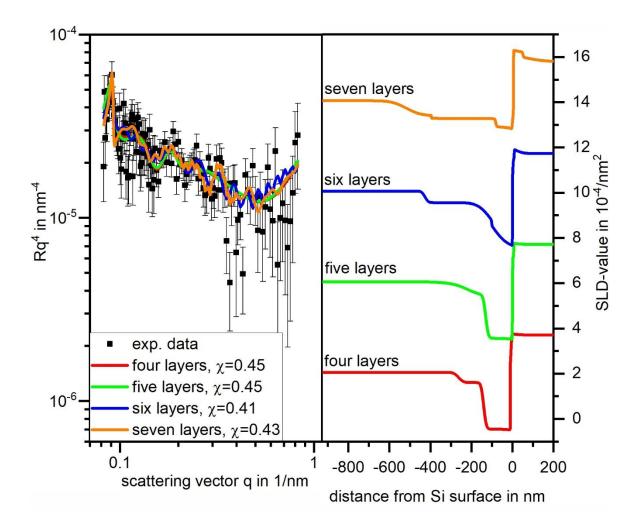

Figure S1: Optimization of the SLD-model. Four different layer-numbers were tested against an intermediate lithiated state. A 6-layer model showed the lowest residuum and was therefore chosen to analyze the data.

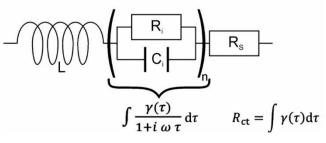

Figure S2: Equivalent circuit used for the analysis of the EIS-measurement. The distribution of relaxation times  $\gamma(\tau)$  is split into a fast ( $\tau < 1.5$  s) and a slow ( $\tau > 1.5$  s) part.

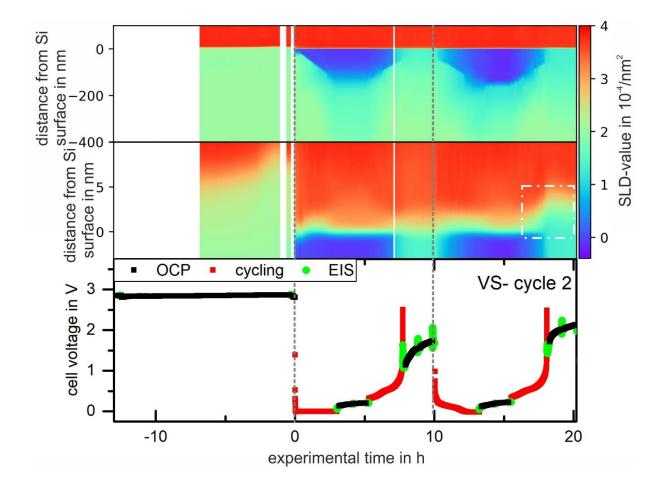

Figure S3: SLD-pattern of the virgin state up to the second cycle. On top the SLD-map of the whole depth is shown, in the middle a zoom-in to the surface. The voltage is shown at the bottom. Dashed lines indicate the beginning of a cycle. The white rectangle indicates the decomposition of the artificial SEI-layer.

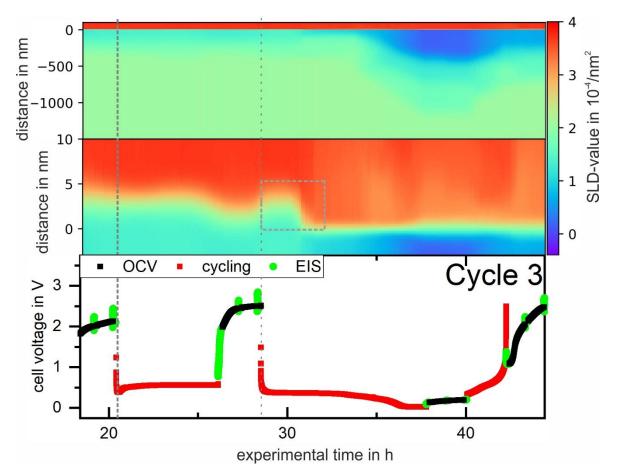

Figure S4: SLD-pattern of the third cycle. On top the SLD-map of the whole depth is shown, in the middle a zoom-in to the surface. The voltage is shown at the bottom. Dashed lines indicate the beginning of a cycle. The grey rectangle indicates the decomposition SEI-layer, which delays the lithiation process.

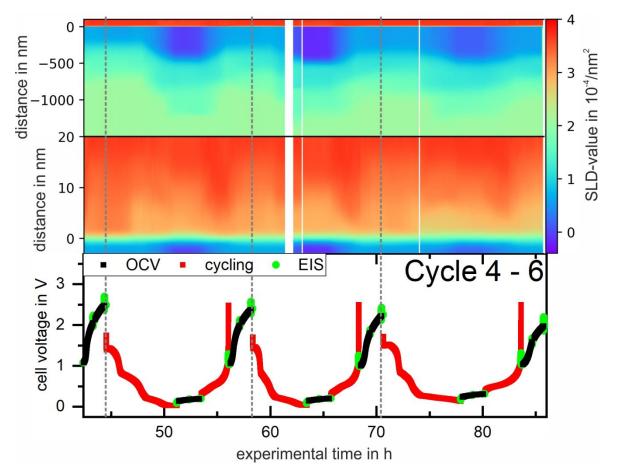

Figure S5: SLD-pattern of the fourth to sixth cycle. On top the SLD-map of the whole depth is shown, in the middle a zoom-in to the surface. The voltage is shown at the bottom. Dashed lines indicate the beginning of a cycle.

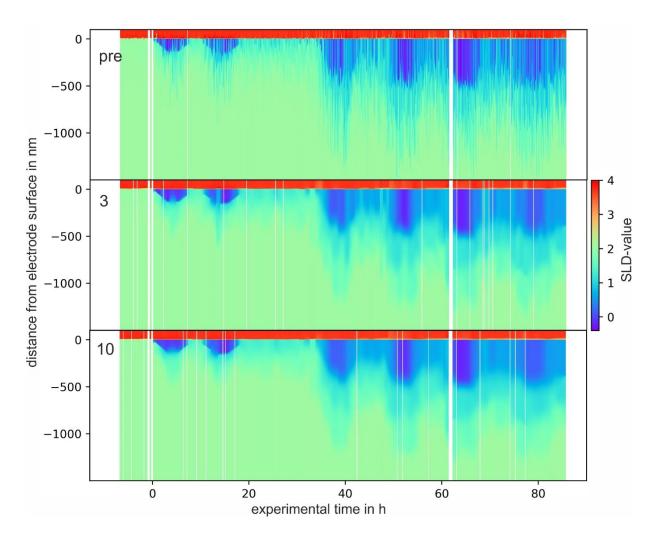

Figure S6: Evolution of the SLD-map during fit-rounds. On top, the SLD-map after the initial fitting is shown without taking neighboring profiles into account. The observed differences between the profiles are not meaningful since they result from a continuous data-acquisition (*operando*-measurement). Therefore the neighboring profiles were taken into account. The resulting SLD-map after 3 and 10 cycles is shown in the middle and at the bottom, respectively. The reflectivity- and charge-residuum do not increase significantly. The white stripes denote the absence of reflectivity data due to beam off periods.

o |Z'| o |Z"|

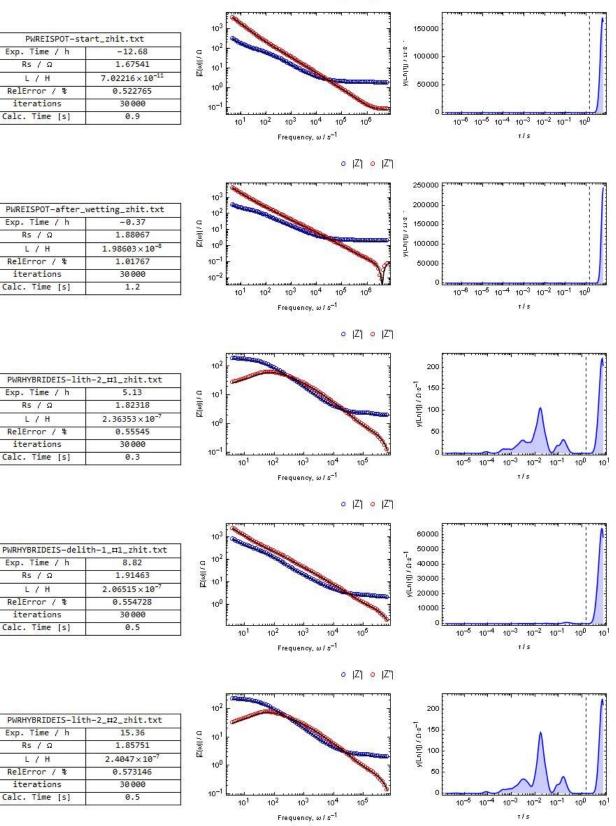

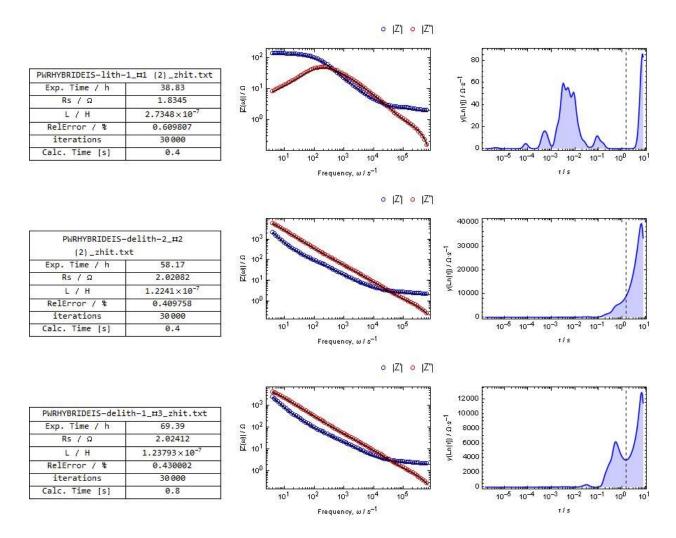

Figure S7: Selection of the EIS analysis results and the corresponding fits.