## Supporting Information

# $\label{eq:constraint} \textbf{Doping-Free All PtSe}_2 \ \textbf{Transistor via Thickness-Modulated}$

### **Phase Transition**

Tanmoy Das<sup>†</sup>, Eunyeong Yang<sup>†</sup>, Jae Eun Seo<sup>†</sup>, Jeong Hyeon Kim<sup>†</sup>, Eunpyo Park<sup>‡</sup>, Minkyung Kim<sup>‡</sup>, Dongwook Seo<sup>†</sup>, Joon Young Kwak<sup>‡</sup>\*, Jiwon Chang<sup>†</sup>\*

<sup>†</sup>Department of Electrical and Computer Engineering, Ulsan National Institute of Science and Technology (UNIST), Ulsan 44919, South Korea

<sup>‡</sup> Center for Neuromorphic Engineering, Korea Institute of Science and Technology (KIST), Seoul 02792, South Korea

E-mail: jykwak@kist.re.kr and jiwon.chang@unist.ac.kr

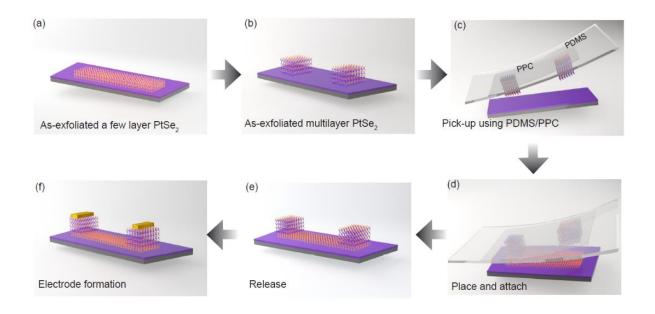

**Figure S1. Fabrication process of PtSe**<sub>2</sub> **FETs using PtSe**<sub>2</sub> **vdW integration. (a-f) Detailed description of the dry transfer.** (a, b) The ultrathin few layer semiconducting PtSe<sub>2</sub> and the thick multilayer PtSe<sub>2</sub> with the intrinsic metallic property were mechanically exfoliated from bulk PtSe<sub>2</sub> crystals on SiO<sub>2</sub>/Si substrate. (c) Pick up: To pick-up the multiplayer PtSe<sub>2</sub> flake, the exfoliated multilayer PtSe<sub>2</sub> flake on SiO<sub>2</sub>/Si substrate was placed under a microscope on a hot stage. A PDMS/PPC polymer block was attached on a slide-glass and held in a micro manipulator and placed above the sample with polymer facing toward the PtSe<sub>2</sub> target. Then, the polymer was brought in close contact with the PtSe<sub>2</sub> flake by lowering the manipulator height until the polymer completely covers the flake. Next, the glass slide was retracted slowly, which picked up the PtSe<sub>2</sub> flake from the SiO<sub>2</sub> on the surface PPC. (d) Placing: The SiO<sub>2</sub>/Si substrate with the exfoliated semiconducting PtSe<sub>2</sub> flake was then placed on a hot stage. The previously picked-up multilayer PtSe<sub>2</sub> flake was aligned over the target few layer semiconducting PtSe<sub>2</sub> flake and precisely controlled to the position over the chosen flake before contacting together. At this point the temperature was elevated to 90 °C and PDMS/PPC proceeded slowly to contact fully. (e) Release:

Subsequently, the glass slide holding the polymer block was slowly moved upward using the micromanipulator. In this manner, the multiplayer PtSe<sub>2</sub> flake on PCC was released and attached onto the semiconducting PtSe<sub>2</sub> flake. (f) Contact fabrication: Metallic multilayer PtSe<sub>2</sub> was finally connected with the conventional Ti/Au metal for the characterization in a back-gated FETs geometry.

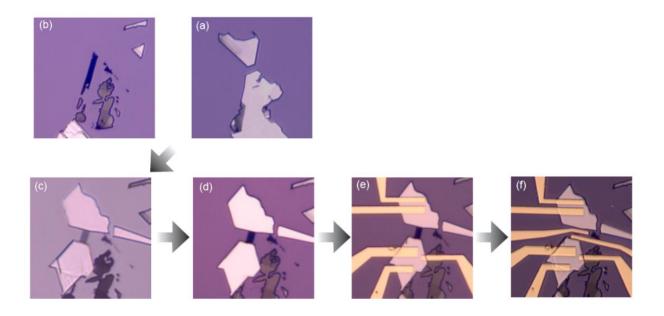

**Figure S2. OM images in sequence showing the fabrication of few layer PtSe<sub>2</sub> FETs with PtSe<sub>2</sub> vdW contact.** (a, b) Exfoliated multilayer and few layer PtSe<sub>2</sub> on SiO<sub>2</sub>/Si substrate. (c) Pickup and place: Two previously exfoliated multilayer PtSe<sub>2</sub> flakes (shown in Figure a) were picked up using PPC at a same time and dropped down on top of the ultrathin semiconducting PtSe<sub>2</sub> flake (shown in Figure b). (d) Release: The dropped-down PtSe<sub>2</sub> flake was adhered by the strong vdW interaction and PPC was removed from the stack. (e, f) Fabricated PtSe<sub>2</sub> vdW contact and Ti/Au contact FETs on the same PtSe<sub>2</sub> flake, respectively.

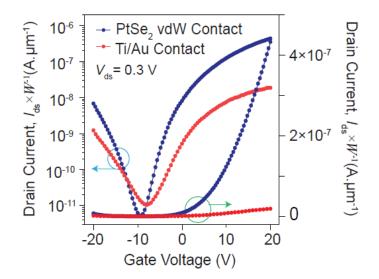

**Figure S3.** Room-temperature semi-logarithmic and linear transfer curve ( $I_{ds}$ - $V_{gs}$ ) comparing few layer PtSe<sub>2</sub> FETs with PtSe<sub>2</sub> vdW contact and Ti/Au contact. The current is normalized by width (*W*). From the width normalized transfer characteristics, the ON current levels could be compared more fairly.

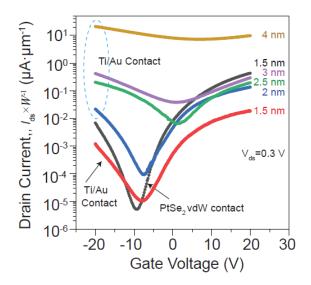

**Figure S4.** Thickness-modulated transport property of PtSe<sub>2</sub> FETs. A progressive transition of electrical transport properties of PtSe<sub>2</sub> FETs with the various thicknesses of PtSe<sub>2</sub> flakes is summarized here. We observed more than six orders increase in the OFF current from ~10<sup>-5</sup> to ~10  $\mu$ A as the thickness varies from ~1.5 to ~4 nm. The n-type conduction property in the thinnest sample was transformed into more symmetrical ambipolar behavior as the thickness increases until there is an appreciable band gap in the PtSe<sub>2</sub> flake. Remarkably, the PtSe<sub>2</sub> devices maintained their typical ambipolar behavior up to ~3 nm, but the insufficient increase in the maximum ON current lowered the current tunability by the gate voltage as the thickness increases. The transfer characteristics finally became independent on the gate voltage in the 4 nm thick PtSe<sub>2</sub> FETs, which is consistent with the decrease in band gap size, indicating the semiconducting to metallic phase transition in PtSe<sub>2</sub>. Interestingly, the representative PtSe<sub>2</sub> vdW contact FETs with the 1.5 nm channel thickness exhibited superior ON current than the ~3 nm thick PtSe<sub>2</sub> FETs with conventional Ti/Au contact.

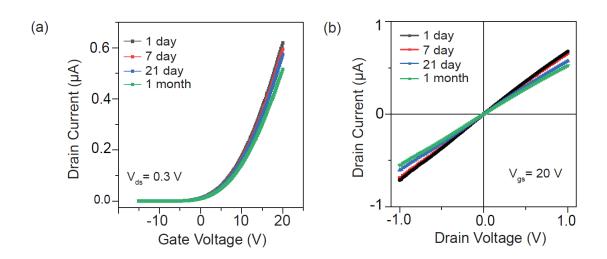

Figure S5. Stability of PtSe<sub>2</sub> vdW contact FETs. (a, b) Typical transfer and output characteristics of few layer PtSe<sub>2</sub> FETs with PtSe<sub>2</sub> vdW contact. Our representative device exhibited a stable device performance over month with minimal degradation in the ON current (~0.6 to ~0.5  $\mu$ A) in the ambient condition. This limited degree of variation in the device performance was possibly due to the degradation in dielectric environments which is independent of 2D materials. It is well known that the metallic phase-engineered TMDs such as 1T-MoS<sub>2</sub> and 1T'-WTe<sub>2</sub> can be severely oxidized by the chemical adsorption of O<sub>2</sub> after the air exposure, resulting in the insufficient ambient stability. Doping induced aging effect and environmental degradation are the two main reason for instability <sup>1</sup>. Our phase transition mediated PtSe<sub>2</sub> vdW contact eliminates the chance of aging related to chemical doping and the intrinsic stability of PtSe<sub>2</sub> resulted to demonstrate long-term stability to air for months only with a minor change in the transfer characteristics which is promising for the potential use of new 2D device architecture.

#### **Contact Resistance Calculation Using the Y-Function Method**

YFM is an effective technique for the low-field mobility ( $\mu_0$ ) extraction utilizing the  $I_{ds}$ - $V_{gs}$  and  $g_m$ - $V_{gs}$  characteristics at low  $V_{ds}$  in the linear region <sup>2</sup>. This method has been extensively adopted in the research of organic thin-film transistors (TFTs) and recently applied in the analysis of MoS<sub>2</sub> based FETs as it can be also used to estimate the contact resistance and the threshold voltage.  $I_{ds}$  and  $g_m$  in the linear region are expressed by the following well known equations:

$$I_{\rm ds} = \frac{W}{L} C_{\rm ox} \mu_{\rm eff} (V_{\rm gs} - V_{\rm th}) V_{\rm ds}$$

$$I_{\rm ds} = \frac{W}{L} C_{\rm ox} \frac{\mu_0}{1 + \theta (V_{\rm gs} - V_{\rm th})} (V_{\rm gs} - V_{\rm th}) V_{\rm ds}$$

(S1)

$$g_{\rm m} = \frac{W}{L} C_{\rm ox} \frac{\mu_0}{[1 + \theta (V_{\rm gs} - V_{\rm th})]^2} V_{\rm ds}$$

(S2)

where *W* and *L* are the effective channel width and length,  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the low-field mobility,  $\theta$  is the mobility attenuation coefficient, and  $V_{th}$  is the threshold voltage. The influence of the mobility attenuation with  $V_{gs}$  can be eliminated by combining the equation S1 and S2 to achieve a simplified function defined as Y-function:

$$Y = \frac{I_{\rm ds}}{\sqrt{g_{\rm m}}} = \sqrt{\mu_0 C_{\rm ox} V_{\rm ds} \frac{W}{L}} (V_{\rm gs} - V_{\rm th}) \tag{S3}$$

The extracted threshold voltage values assist to determine the mobility reduction factor related to the contact resistance, surface roughness, and phonon scattering which can be expressed by:

$$\theta = \left[\frac{I_{\rm ds}}{\left(g_{\rm m}(V_{\rm gs} - V_{\rm th})\right)} - 1\right] / (V_{\rm gs} - V_{\rm th}) \tag{S4}$$

In strong inversion, this function is expected to be a constant equal to the value of the mobility reduction coefficient. The mobility attenuation factor  $\theta$  described in equation S1, S2 and S4 is  $\theta$  =

$\theta_{ch}+\theta_c = \theta_{ch}+R_c\mu_0C_{ox}W/L$ , where  $\theta_{ch}$  is the mobility attenuation factor from the channel related to the surface roughness and phonon scattering and  $\theta_c$  is the mobility attenuation factor due to contact. In absence of  $\theta_{ch,,}$  the upper limit of  $R_c$  can be extracted eventually from the expression,  $R_c = \frac{\theta_{ch,,}}{\mu_0 C_{ox}} \frac{L}{W}$ .

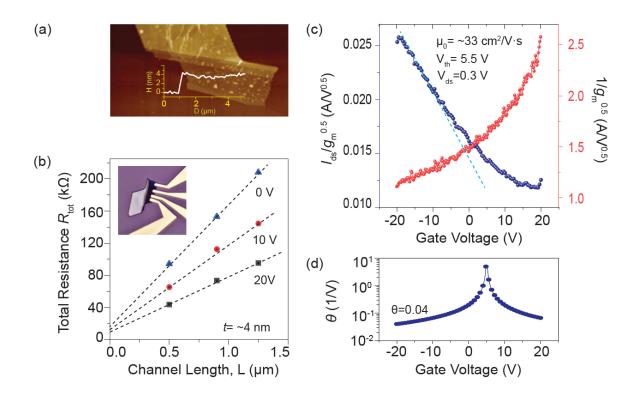

Figure S6. Comparison of the contact resistance ( $R_c$ ) in a 4 nm thick PtSe<sub>2</sub> FETs by TLM and YFM. (a) AFM image of a 4 nm thick PtSe<sub>2</sub> flake with the corresponding height profile in the inset. (b) Total device resistance ( $R_{tot}$ ) vs. channel length (L) measured by TLM, for different  $V_{gs}$ . Linear extrapolation of  $R_{tot}$  vs. L in the vertical y-axis intercept provides the estimation of  $R_c$  of ~6  $k\Omega \cdot \mu m$  for a 4 nm thick PtSe<sub>2</sub> FETs with Ti/Au contact. (c) Extraction of  $R_c$  for the same 4 nm PtSe<sub>2</sub> FETs using YFM for direct comparison. The threshold voltage and low-field mobility were estimated as 5.5 V and ~33 cm<sup>2</sup>/V·s from the interception and slope of  $\frac{I_{ds}}{\sqrt{G_m}}$  vs.  $V_{gs}$ , respectively.

(d) The mobility reduction coefficient ( $\theta$ ) vs.  $V_g$  plot. With,  $\theta = R_c \mu_0 C_{ox} W/L$ ,  $R_c$  of 43 k $\Omega$ · $\mu$ m was extracted from the strong inversion region. This result suggests that YFM overestimated  $R_c$  for the same device and yielded ~7 times higher  $R_c$  compared to TLM.

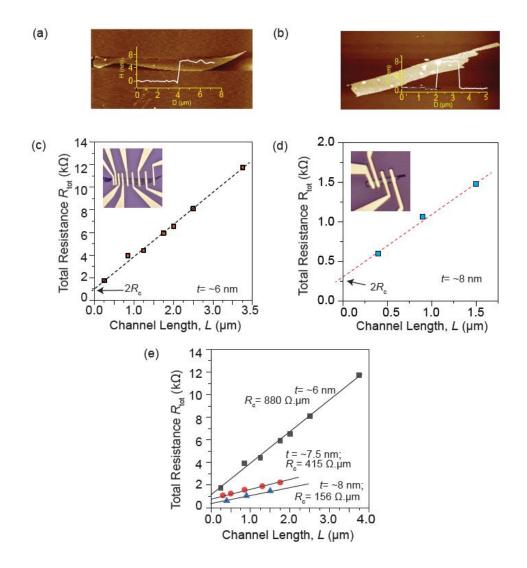

Figure S7. Contact resistance ( $R_c$ ) extraction of PtSe<sub>2</sub> FETs with Ti/Au contact for various PtSe<sub>2</sub> channel thicknesses. (a, b) AFM images of various PtSe<sub>2</sub> flakes used for TLM measurement. Inset is the corresponding line profile of the particular flake, showing that the thickness of the PtSe<sub>2</sub> channel is ~6 and ~8 nm, respectively. (c, d) The results of TLM measurements for Ti/Au contact FETs. Corresponding OM images of the fabricated multilayer PtSe<sub>2</sub> TLM structure is shown in the inset. The contact resistance can be extracted from the y

intercept of the linear fit to the total resistance as a function of the channel length. As predicted theoretically, being metallic in nature, both the ~8 and ~6 nm thick  $PtSe_2$  devices exhibit perfectly linear  $I_{ds}$ - $V_{ds}$  behaviors without any gate dependence. (e) The extracted contact resistances from the various thicknesses of  $PtSe_2$  flakes are summarized and the result shows that the contact resistance as low as ~150  $\Omega$ ·µm for a ~8 nm thick  $PtSe_2$  can be achieved.

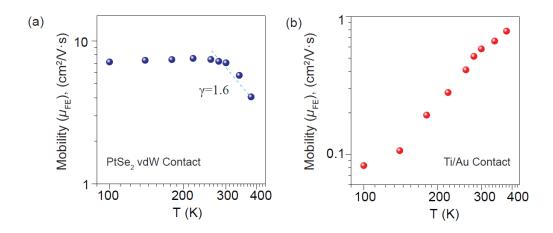

**Figure S8.** (a, b) Temperature-dependent field-effect mobility ( $\mu_{FE}$ ) of PtSe<sub>2</sub> vdW contact and Ti/Au contact devices. Mobility *vs.* temperature for PtSe<sub>2</sub> vdW contact reveals that calculated mobility remained almost saturated at low temperature due to charge impurity scattering. At high temperature (over 240 K), mobility started to decrease with the increasing temperature because of optical phonon scattering which can be fitted by a generic power law of  $\mu_{FE} \sim T^{\gamma}$  where  $\gamma \approx 1.6$ . This trend is consistent with the behavior of mobility limited by optical phonon scattering in other 2D TMDs <sup>3</sup>. On the contrary, mobility for conventional Ti/Au contact rapidly increased from 0.09 to 0.76 cm<sup>2</sup>/V·s with the increasing temperature. The temperature-dependent increase of mobility implies a thermionic emission dominant carrier transport in Ti/Au contact possibly due to the existence of a higher SBH.

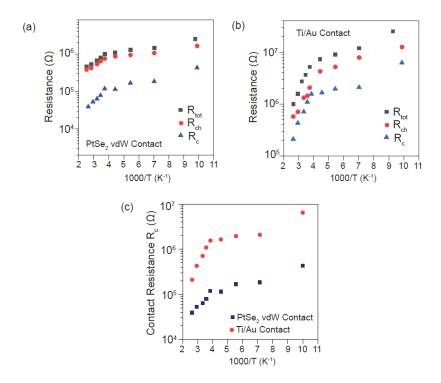

Figure S9. Extraction of temperature-dependent total resistance ( $R_{tot}$ ), channel resistance ( $R_{ch}$ ), and contact resistance ( $R_c$ ) for PtSe<sub>2</sub> vdW contact and Ti/Au contact devices. (a, b) Total resistance ( $R_{tot}$ ; squares), channel resistance ( $R_{ch}$ ; circle) and contact resistance ( $R_c$ ; triangle) as function of 1000/T for PtSe<sub>2</sub> vdW contact and Ti/Au contact devices, respectively. The channel resistance can be extracted from temperature-dependent  $I_{ds}$  measurement in Figure 5a and b, using following expression:

$$R_{\rm ch}(T) = \frac{1}{qn\mu(T)} \frac{L}{Wt}$$

where q is the elementary charge,  $n = \left(\frac{C_{ox}}{q}\right) (V_{gs} - V_{th})/t$  is the carrier density where t is the channel thickness, and  $\mu(T)$  is the temperature dependent mobility of the device. The total resistance was calculated simply by using  $R_{tot} = V_{ds}/I_{ds}$  at  $V_{ds} = 0.3$  V and  $V_{gs} = 20$  V, where channel resistance turns out to be insignificant. Henceforth,  $R_c$  is computed by  $(R_{tot}-R_{ch})/2$  for each temperature. (c) Comparison of contact resistance for PtSe<sub>2</sub> vdW contact and Ti/Au contact FETs.

It was found that PtSe<sub>2</sub> vdW contact device shows one order magnitude lower contact resistance compared to the Ti/Au contact device.

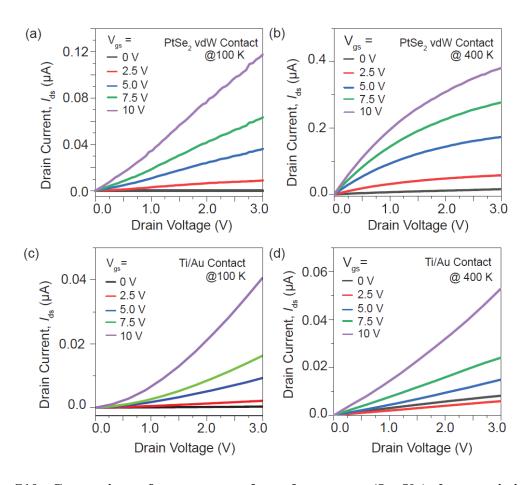

Figure S10. Comparison of temperature-dependent output ( $I_{ds}-V_{ds}$ ) characteristics of PtSe2 vdW contact and Ti/Au contact FETs. Output characteristics of the both devices were measured at 100 and 400 K, respectively. (a, b) Typical output characteristics in PtSe<sub>2</sub> vdW contact FETs at low temperature reveals that output curves maintained their linearity even at 100 K, suggesting the absence of a contact barrier whereas an excellent current saturation can be observed at 400 K which implies the true ohmic behavior. (c, d) In contrast, Ti/Au contact FETs clearly shows current crowding at low  $V_{ds}$  due to the large contact resistance and non-saturated output curve at high

temperature which further implies the existence of significant SB compared to the PtSe<sub>2</sub> vdW contact devices.

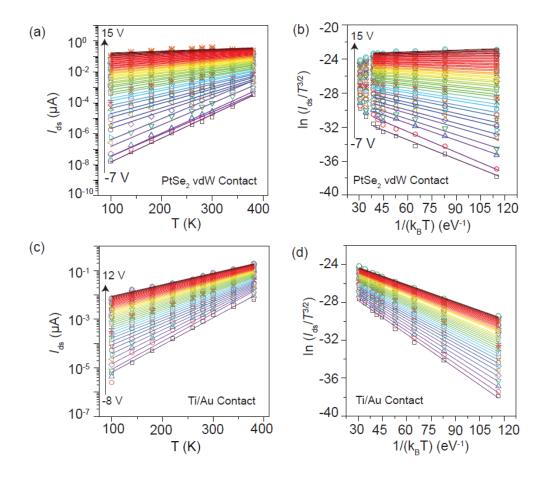

Figure S11. Temperature-dependent transport for PtSe<sub>2</sub> vdW contact and Ti/Au contact FETs in the thermionic emission model. The thermionic emission equation is simplified to  $I_{ds} = \left[A^* T^{3/2} \exp\left(-\frac{q\Phi_{\rm SB}}{k_{\rm B}T}\right)\right]$  for  $qV_{\rm ds} \gg k_{\rm B}T$ . In the sub-threshold regime the transistor behavior can be expressed as  $I_{ds} = \left[A^* T^{3/2} \exp\left(-\frac{q\Phi_{\rm bi}}{k_{\rm B}T}\right)\right]$ , where  $\Phi_{\rm bi}$  is the built in potential. At the flat-band condition,  $q\Phi_{\rm bi}$  becomes equal to  $q\Phi_{\rm SB}^{-4}$ . (a, c) Temperature-dependent semi-logarithmic current  $I_{\rm ds}$  vs. temperature T plot for PtSe<sub>2</sub> vdW contact and Ti/Au contact FETs. (b, d) Corresponding linear fit to the Arrhenius plot of  $\ln(I_{\rm ds}/T^{3/2})$  vs.  $1/k_{\rm B}T$  at various  $V_{\rm gs}$  for PtSe<sub>2</sub> vdW contact and

Ti/Au contact FETs, respectively. The SBH estimated from the slope of a linear fit are shown in Figure 5e and f.

| Preparation<br>Method                             | PtSe2<br>thicknes<br>s (nm) | Electrode<br>Material | Fabrication<br>method                      | Carrier<br>type | ON/OFF<br>ratio | $\begin{array}{c} \text{Mobility} \\ [\text{cm}^2  \text{V}^{-1} \\ \text{s}^{-1}] \end{array}$ | Rc                         | SBH<br>[meV]                | Ref.         |

|---------------------------------------------------|-----------------------------|-----------------------|--------------------------------------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|--------------|

| mechanical exfoliation                            | 2-5                         | Pd                    | e-beam<br>lithography                      | n               | 10 <sup>5</sup> | 3                                                                                               | NA                         | NA                          | 5            |

| CVD                                               | 1.6                         | Au                    | direct laser<br>write                      | р               | 40              | 5–9                                                                                             | 600 kΩ.µm                  | NA                          | 6            |

|                                                   |                             |                       |                                            | n               | 25              | 6–12                                                                                            | 200 kΩ.µm                  |                             |              |

| CVT                                               | 11                          | Ti/Au                 | e-beam<br>lithography                      | n               | 200             | 210                                                                                             | NA                         | NA                          | 7            |

| TAC and<br>transfer<br>to secondary<br>substrates | 2.5-3                       | Ni/Au                 | e-beam<br>lithography                      | р               | 230             | 0.3,<br>10 (after<br>correctio<br>n)                                                            | $1.65	imes10^{6}$ $\Omega$ | E <sub>A</sub> =20<br>0 meV | 8            |

| Vapor-phase selenization                          | 3                           | Ni/Au                 | shadow<br>mask                             | р               | 30              | 3.5                                                                                             | 184 kΩ.µm                  | NA                          | 9            |

| Plasma<br>assisted<br>selenization                | 2.5                         | Pt                    | Photo-<br>lithography                      | р               | 16              | 0.7                                                                                             | NA                         | NA                          | 10           |

| Thermally<br>assisted<br>selenization             | 4                           | Al                    | Photo-<br>lithography                      | р               | 1.9             | 3                                                                                               | 3 kΩ.µm                    | NA                          | 11           |

| Mechanical exfoliation                            | 3                           | PtSe <sub>2</sub>     | ICP RIE, e-<br>beam<br>lithography         | р               | 93              | 150                                                                                             | 0.3 kΩ.µm                  | NA                          | 12           |

| Mechanical exfoliation                            | 1.5                         | PtSe <sub>2</sub>     | Dry<br>Transfer, e-<br>beam<br>lithography | n               | 105             | 7.5                                                                                             | 93 kΩ∙µm                   | 35                          | This<br>Work |

Table S1. Comparison of recently reported PtSe<sub>2</sub> FETs with different contact materials

Missing values are represented by NA (not available). Data are from refs  $^{5\text{-}12}$

#### References

- Kung, Y. C.; Hosseini, N.; Dumcenco, D.; Fantner, G. E.; Kis, A. Air and Water-Stable n-Type Doping and Encapsulation of Flexible MoS<sub>2</sub> Devices with SU8. *Adv. Electron. Mater.* **2019**, *5* (1), 1–7. https://doi.org/10.1002/aelm.201800492.

- (2) Ghibaudo, G. New Method for the Extraction of MOSFET Parameters Indexing. *Electron. Lett.* **1988**, *24* (9), 543–545. https://doi.org/10.1049/el:19880369.

- (3) Radisavljevic, B.; Kis, A. Mobility Engineering and a Metal–Insulator Transition in Monolayer MoS<sub>2</sub>. *Nat. Mater.* **2013**, *12* (9), 815–820. https://doi.org/10.1038/nmat3687.

- (4) Allain, A.; Kang, J.; Banerjee, K.; Kis, A. Electrical Contacts to Two-Dimensional Semiconductors. *Nat. Mater.* **2015**, *14* (12), 1195–1205. https://doi.org/10.1038/nmat4452.

- (5) Ciarrocchi, A.; Avsar, A.; Ovchinnikov, D.; Kis, A. Thickness-Modulated Metal-to-Semiconductor Transformation in a Transition Metal Dichalcogenide. *Nat. Commun.* 2018, 9 (1), 919. https://doi.org/10.1038/s41467-018-03436-0.

- Xu, H.; Zhang, H.; Liu, Y.; Zhang, S.; Sun, Y.; Guo, Z.; Sheng, Y.; Wang, X.; Luo, C.; Wu, X.; Wang, J.; Hu, W.; Xu, Z.; Sun, Q.; Zhou, P.; Shi, J.; Sun, Z.; Zhang, D. W.; Bao, W. Controlled Doping of Wafer-Scale PtSe<sub>2</sub> Films for Device Application. *Adv. Funct. Mater.* 2019, 29 (4), 1805614. https://doi.org/10.1002/adfm.201805614.

- (7) Zhao, Y.; Qiao, J.; Yu, Z.; Yu, P.; Xu, K.; Lau, S. P.; Zhou, W.; Liu, Z.; Wang, X.; Ji, W.; Chai, Y. High-Electron-Mobility and Air-Stable 2D Layered PtSe<sub>2</sub> FETs. *Adv. Mater.* 2017, 29 (5), 1604230. https://doi.org/10.1002/adma.201604230.

- (8) Ansari, L.; Monaghan, S.; McEvoy, N.; Coileáin, C. Ó.; Cullen, C. P.; Lin, J.; Siris, R.; Stimpel-Lindner, T.; Burke, K. F.; Mirabelli, G.; Duffy, R.; Caruso, E.; Nagle, R. E.; Duesberg, G. S.; Hurley, P. K.; Gity, F. Quantum Confinement-Induced Semimetal-to-Semiconductor Evolution in Large-Area Ultra-Thin PtSe<sub>2</sub> Films Grown at 400 °C. *npj 2D Mater. Appl.* **2019**, *3* (1), 33. https://doi.org/10.1038/s41699-019-0116-4.

- (9) Yim, C.; Lee, K.; McEvoy, N.; O'Brien, M.; Riazimehr, S.; Berner, N. C.; Cullen, C. P.; Kotakoski, J.; Meyer, J. C.; Lemme, M. C.; Duesberg, G. S. High-Performance Hybrid Electronic Devices from Layered PtSe<sub>2</sub> Films Grown at Low Temperature. *ACS Nano* 2016, 10 (10), 9550–9558. https://doi.org/10.1021/acsnano.6b04898.

- (10) Su, T.-Y.; Medina, H.; Chen, Y.-Z.; Wang, S.-W.; Lee, S.-S.; Shih, Y.-C.; Chen, C.-W.; Kuo, H.-C.; Chuang, F.-C.; Chueh, Y.-L. Phase-Engineered PtSe 2 -Layered Films by a Plasma-Assisted Selenization Process toward All PtSe<sub>2</sub> -Based Field Effect Transistor to Highly Sensitive, Flexible, and Wide-Spectrum Photoresponse Photodetectors. *Small* **2018**, *14* (19), 1800032. https://doi.org/10.1002/smll.201800032.

- (11) Li, L.; Xiong, K.; Marstell, R. J.; Madjar, A.; Strandwitz, N. C.; Hwang, J. C. M.; McEvoy, N.; McManus, J. B.; Duesberg, G. S.; Goritz, A.; Wietstruck, M.; Kaynak, M. Wafer-Scale Fabrication of Recessed-Channel PtSe<sub>2</sub> MOSFETs With Low Contact Resistance and Improved Gate Control. *IEEE Trans. Electron Devices* **2018**, *65* (10), 4102–4108. https://doi.org/10.1109/TED.2018.2856305.

- (12) Yang, Y.; Jang, S. K.; Choi, H.; Xu, J.; Lee, S. Homogeneous Platinum Diselenide Metal/Semiconductor Coplanar Structure Fabricated by Selective Thickness Control. *Nanoscale* **2019**, *11* (44), 21068–21073. https://doi.org/10.1039/C9NR07995E.