# Wafer-Scale Assembly of Highly Ordered Semiconductor Nanowire Arrays by Contact Printing

Zhiyong Fan<sup>1,2</sup>, Johnny C. Ho<sup>1,2</sup>, Zachery A. Jacobson<sup>1,2</sup>, Roie Yerushalmi<sup>1,2</sup>, Robert L. Alley<sup>1</sup>, Haleh Razavi<sup>1</sup>, Ali Javey<sup>1,2,\*</sup>

- Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720.

- Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

## **Supporting Information**

<sup>\*</sup> Correspondence to: ALI JAVEY ajavey@eecs.berkeley.edu

#### NANOWIRE GROWTH

Si, Ge and core/shell Ge/Si NWs were grown in a custom built CVD system using previously reported vapor-liquid-solid process. Monodispersed gold nanoparticles with d=10-100 nm (Ted Pella, Inc.) were used as catalytic seeds on a Si/SiO<sub>2</sub> (50 nm) substrates. The typical surface density of the deposited Au nanoparticles was ~20  $\mu$ m<sup>-2</sup>. *p*-type SiNWs were grown at 460 °C and 30 torr pressure under a constant flow of silane (4 s.c.c.m.), hydrogen (15 s.c.c.m.), and diborane (0.01% balanced H<sub>2</sub>, 5 s.c.c.m.) for 15 minutes, resulting in ~120  $\mu$ m long NWs. GeNWs were grown at 280 °C and 45 torr with the use of germane (10% balanced in H<sub>2</sub>, 15 s.c.c.m.) as the precursor gas. Under this growth condition, a growth rate of ~ 1  $\mu$ m/min was observed. Core/shell Ge/Si NWs were synthesized by depositing a thin crystalline Si shell (~ 5nm) on the GeNWs that were grown using the above condition. The Si shell was deposited at 430 °C under a flow of 2 s.c.c.m. SiH<sub>4</sub> and 15 s.c.c.m. H<sub>2</sub> at 2.8 torr for 10 minutes.

#### SURFACE FUNCTIONALIZATION OF RECIEVER SUBSTRATES

Surface modification of Si/SiO<sub>2</sub> (50 nm) substrates was achieved by well-established siloxane-based condensation chemistry of various compounds including (heptadecafluoro-1,1,2,2-tetrahydrodecyl) dimethylchlorosilane (Gelest, Inc.), N-trimethoxysilylpropyl-N,N,N-trimethylammonium chloride (Gelest, Inc.), and 3-Triethoxysilylpropylamine (Sigma-Aldrich, Inc.) to define -CF<sub>3</sub>, -N(Me)<sub>3</sub><sup>+</sup>, or -NH<sub>2</sub> terminated surfaces, respectively. To carry out the reactions, solutions of ~0.5 vol% of the above compounds were prepared with either hexane or ethanol as the solvent. Si/SiO<sub>2</sub> substrates were then reacted with the respective solutions for 45 min, followed by a

thorough wash with the solvent and baking at 120°C for 20 min. For the poly-L-lysine functionalization, the substrate was coated with ~0.1% w/v of poly-L-lysine in water (Ted Pella, Inc.) for 5 min, and was then thoroughly rinsed with DI water. Notably, the poly-L-lysine functionalization can be carried out directly on top of the photolithographically patterned substrate since it does not react with the Shipley 1805 photoresist.

#### NANOWIRE PRINTING

The receiver substrate was patterned by photo (Shipley, 1805 resist) or electron beam lithography (PMMA 495 C2, diluted 50% in chlorobenzene) to define the assembly regions with the desired width and length, and was then mounted on a fixed stage and covered with a 2:1, v:v mixture of octane and mineral oil to serve as a lubricant. The donor (growth) substrate, consisting of a lawn of NWs was cut into the desired dimension and mounted on a metal weight. The weight was chosen so that it provides a pressure of ~ 10 g/cm<sup>2</sup>. The donor chip, along with the weight, was then gently brought into contact on the receiver substrate, such that the donor and receiver substrates directly face each other with the edge of the donor chip ~0.5 mm away from the edge of the pattern of the receiver substrate. The weight, and therefore the donor substrate, was then pushed by a micromanipulator for ~0.5 mm with a constant velocity of ~20 mm/min in the direction parallel to the resist patterns of the receiver substrate. A second weight was then added to the donor chip in order to increase the total pressure to ~20 g/cm<sup>2</sup>. The sliding was then continued with the same velocity of ~20 mm/min until the donor chip passed over the entire pattern of the receiver substrate. The donor chip and the weights were then gently removed and the receiver substrate was rinsed well in octane. Note that our double weight approach is used to avoid mechanical "stamping" of NWs at the initial stage when the two substrates are brought in contact. Important care was taken to ensure no dust particles were found on either of the two substrates prior to the contact printing process. For all of our presented contact printing results, we used donor substrates with high NW density (>10 NW/ $\mu$ m<sup>2</sup>).

#### NANOWIRE ARRY DEVICE FABRICATION AND CHARACTERIZATION

Source/drain electrodes were patterned with photolithography (Karl Suss MA6 Mask Aligner) on top of the contact printed NWs on both Kapton (DuPont) and Si/SiO<sub>2</sub> substrates, followed by lift-off. For Ge/Si NW array FETs, Ni (5nm)/Pd(45nm) metal films were deposited by electron beam evaporation. The spacing between source and drain electrodes is ~2 µm. For the electrical measurements, heavily doped Si substrate was used as a global back-gate. For SiNW Schottky diodes, two separate lithography and metallization processes were carried out to obtain Pd (50 nm) and Al (50 nm) asymmetric contacts on the printed SiNWs (d~30 nm) with a flexible Kapton substrate. The Kapton substrate was coated with SU8 (Shipley) followed by deposition of ~25 nm SiO<sub>2</sub> (e-beam evaporation) to improve the surface quality for contact printing. The surface was then coated with poly-L-lysine to enhance the printed NW density. After fabrication, the electrical transport properties of the devices were investigated with a probe station system (Signatone) and semiconductor parameter analyzer (Agilent 4155C) at room temperature.

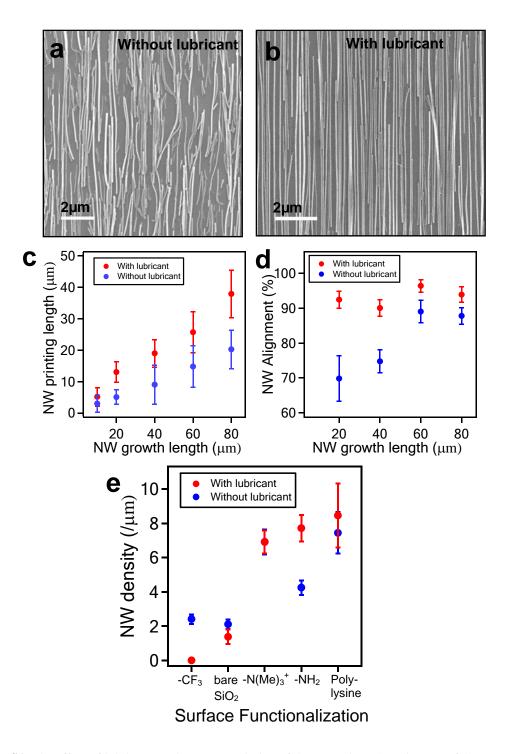

#### THE ROLE OF LUBRICANT

Through systematic studies, we have explored the role of lubricant (2:1, v:v octane and mineral oil mixture) on the contact printing of nanowires. We find that the use of lubricant is essential for achieving highly dense, long, and well aligned parallel arrays of nanowires (Fig. S1). The lubricant serves as a spacing layer, minimizing the friction between the receiver and donor substrates, and NW-NW interactions; therefore, reducing the uncontrolled transfer of the nanowires due to mechanical coupling. This is quite evident in the surface functionalization studies, where significantly lower density contrast is observed for the dry transfer as compared to the lubricated transfer (Fig S1e). For instance, for the fluorinated (highly non-sticky) receiver substrates, which show weak chemical bonding interactions with nanowires, a density of  $<10^{-3}$  NW/ $\mu$ m is obtained when lubricant is used while a density of <2NW/ $\mu$ m is observed for the dry printing.

**Figure S1.** The effect of lubricant on the contact printing of the nanowires. SEM images of GeNW printing without (a) and with (b) lubricant, clearly showing the impact of the lubricant in obtaining highly aligned and ordered NWs. (c) The average length and (d) orientation alignment of the printed GeNWs as a function of their original length on the growth substrate for contact printing with and without lubricant. For (a)-(d) the receiver substrate was functionalized with poly-L-lysine. (e) Nanowire printing density of GeNWs (d~15 nm) as a function of the surface functionalization of the receiver substrate.

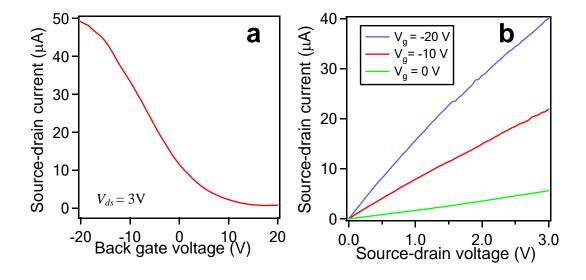

### ELECTRICAL CHARACTERIZATION OF PARALLEL ARRAY NW FETS

Core/shell Ge/Si nanowires were printed to form high density and well aligned parallel arrays. Subsequently, the NW arrays were used to fabricate back-gated FETs as shown in the main content. Figure S2 shows the electrical properties of a representative FET fabricated on a ~10 µm wide NW film, consisting of ~50 NWs (5 NWs/µm). It shows a clear *p*-type transistor behavior with a linear transconductance of ~2.3µA/V. The modest transconductance originates from the back gate structure with relatively thick gate dielectric (50 nm SiO<sub>2</sub>), and in the future, it can be readily improved through high-k dielectric and metal top gate integration, and channel length scaling.<sup>32</sup>

**Figure S2.** Electrical Characteristics of Ge/Si core/shell NWs. (a)  $I_{ds}$ - $V_{gs}$  and (b)  $I_{ds}$ - $V_{ds}$  characteristics of a representative FET fabricated on a parallel array of printed nanowires with a channel width of ~10  $\mu$ m (~50 NWs).