#### **Supporting Information**

# Forming-Less Compliance-Free Multi-State Memristors as Synaptic Connections for Brain-Inspired Computing

Sien Ng<sup>1</sup>, Rohit Abraham John<sup>1</sup>, Jing-ting Yang<sup>1</sup>, Nripan Mathews<sup>1,2\*</sup>

<sup>1</sup>School of Materials Science and Engineering, Nanyang Technological University, 50 Nanyang Avenue, Singapore 639798

<sup>2</sup>Energy Research Institute @ NTU (ERI@N), Nanyang Technological University, Singapore 637553

### Corresponding Author: Nripan Mathews (nripan@ntu.edu.sg)

Keywords: forming-less, compliance-free, analog memory window, multi-state memristors,

artificial synapses

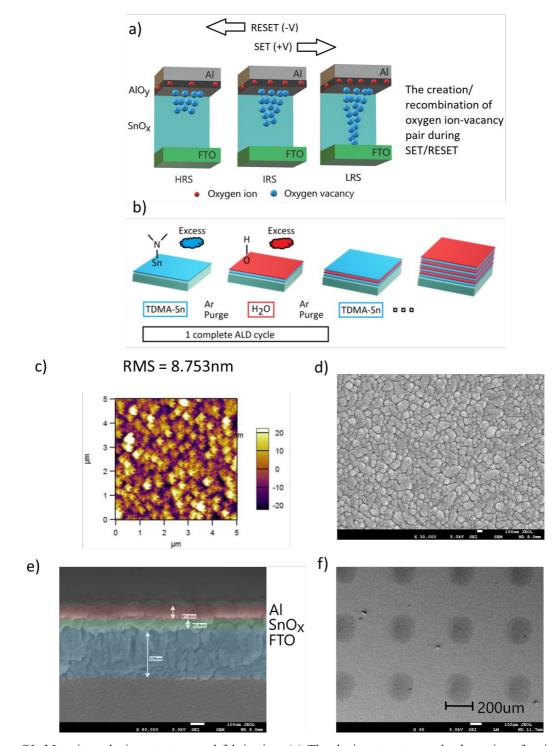

**Figure S1.** Memristor device structure and fabrication. (a) The device structure and schematics of switching mechanism involving a possible filamentary conduction during SET operation and the recombination of ion-vacancy during RESET operation. (b) Self-limiting half-reactions involved in the conformal and uniform ultrathin  $SnO_x$  thin film atomic layer deposition (ALD). (c) Atomic force microscopy (AFM) height retrace image of the deposited  $SnO_x$  thin film on FTO substrate shows an RMS roughness of ~9nm. (d) Top-down scanning electron microscopy image of pinhole-free  $SnO_x$  thin film. (e) Cross-sectional scanning electron microscopy image of  $Al/SnO_x/FTO$ . (f) Top-down scanning electron microscopy image of Al electrode area of device.

Aluminium with a high standard reduction potential was chosen as the top electrode overlaying the active  $SnO_x$  switching matrix grown on a highly conductive FTO substrate. The presence of an oxygen getter electrode readily captures oxide ions during the SET operation of the memristor, preventing an abrupt switching transition. As a result, a self-compliance phenomenon followed by gradual switching characteristics is observed in the multi-level memristor. During the RESET operation, the recombination of the oxygen vacancies with the oxide ions close to the interface results in the reduction of filamentary length (Figure S1a).

To improve the reliability of the memristor device fabrication, atomic layer deposition (ALD) process was selected to ensure a uniform and conformal thin film. The ALD process involves self-limiting half-reactions which are the initial chemisorption of Sn precursor molecules and the subsequent oxidation of the chemisorbed Sn species (Figure S1b). Such layer-by-layer deposition ensures conformal growth along the rough FTO polycrystalline surface. FTO glass was chosen as the bottom electrode due to its chemical inertness, temperature stability and high conductivity. The AFM image indicates the conformality of the SnO<sub>x</sub> across the FTO substrate (Figure S1c). In Figure 1e, we can observe the thicknesses of individual layers from the cross-sectional image.

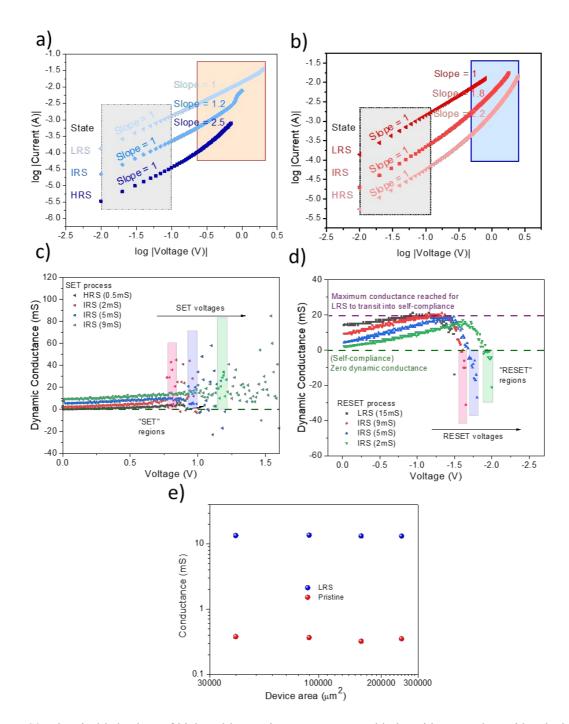

**Figure S2.** Electrical behaviour of high and low resistance states. Double logarithm I-V plots with calculated slopes for gradual (a) potentiation and (b) depression operation. Dynamic conductance with respect to applied voltage for (c) SET operation and (d) RESET operation, comparing transition points between various conductance states. (e) Areal independency of programming the conductance states, indicating the possible filamentary nature of conduction.

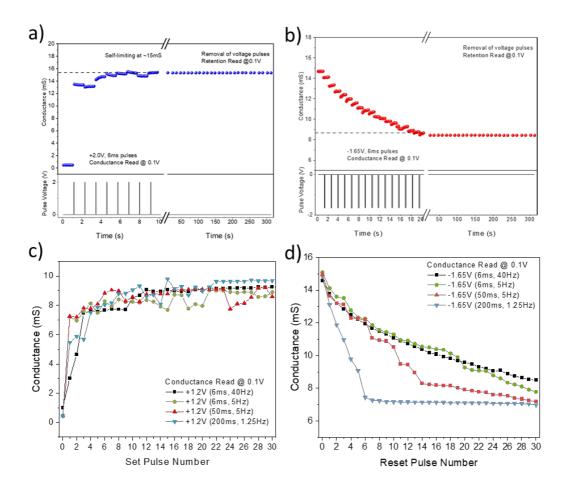

**Figure S3.** Pulse measurements for long-term plasticity. (a) Potentiation pulses of +2V to reach 15mS self-limit and non-volatile state. (b) Depression pulses of -1.65V to reach 9mS non-volatile state. The effect of duty cycle (Pulse width and frequency for (c) +1.2V potentiation and (d) -1.65V depression.

In addition to varying pulse voltage, we also studied the effect of stimulation duty cycle (pulse width and frequency) on the conductance updates. With increasing pulse width, the conductance update is expected to increase in magnitude and digital character. However, in Supporting Figure S3a, changing the pulse width from 6ms to 200ms does not affect the conductance update significantly for the potentiation operations, suggesting that 6ms is long pulse for potentiation. In contrast, the depression operation underwent a transition from analogue to digital regime. Increasing the pulse width resulted in less programmable states for the depression operations. Interestingly, increasing the pulse width did not significantly lower the conductance soft boundary for -1.65V depression pulses. The conductance for all duty

cycles slowly approach the conductance of approximately 7mS. However, the frequency of stimulation did not significantly affect the conductance updates in both potentiation and depression."

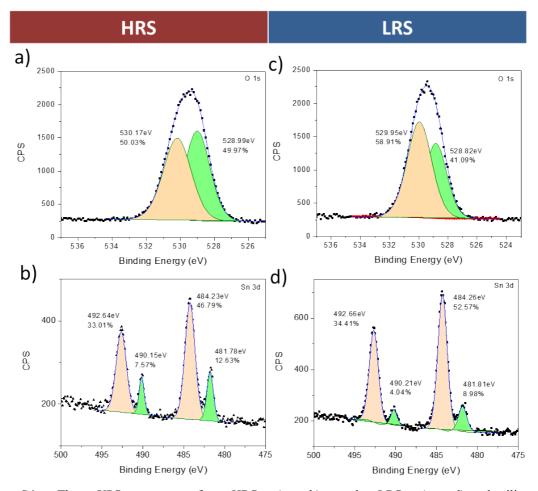

Figure S4. The XPS spectra for HRS (a, b) and LRS (c, d) detailing the O 1s and Sn 3d peaks. (a and c) O 1s peaks- the signal at ~529.0eV is attributed to the low binding energy of fully coordinated lattice oxygen of SnO2, while the left-shifted signal at ~530.0eV is attributed to the oxygen vacancies with higher binding energy. (b and d) Sn 3d peaks- the doublets are visible with a doublet shift of ~8.4eV and an aerial ratio of 2:3. Metallic Sn is identified at ~490.2eV with the oxidised  $Sn^{2+}/Sn^{4+}$  at 2.5eV shifted to the left.

A thin layer of Al (~5nm) was evaporated specifically for the XPS measurement. The thin layer of Al electrode allows for both electrical stimulation and  $SnO_2$  chemical signals to be picked up. Monochromatic Al K $\alpha$  is used as X-ray source and helps to reduce FWHM and improve resolution of the signals. Selective area mode is used with a small aperture at the collector. This

allows an analysis area of  $55\mu$ m, which is within our electrode size of  $200\mu$ m. The take-off angle is selected to be ~60° for optimum signal collection. The interaction depth is expected to be 7 to 11nm based on excitation wavelength of Al K $\alpha$  and the photoelectron take-off angle.

2 devices each for LRS and HRS are electrically SET/RESET prior to XPS measurements and loaded into the ultra-high vacuum (10<sup>-8</sup> torr) chamber. The evolution of metallic Sn peak could arise from the reduction of SnO<sub>2</sub> thin film by the reactive Al electrode during the deposition process (Figures S3b and d). Such a reduction can be observed at metal/metal-oxide interfaces where the metal is of higher reduction potential than the oxide. The reduction potential differences can be determined from the thermodynamic series used in metallurgy such as Ellingham diagram<sup>1</sup>. This correlation allows for further modulation of the memristive characteristics in future by adopting active electrodes with the desired oxygen-gettering ability, paving way for novel memristive devices and architectures. To investigate the composition ratio of SnO<sub>x</sub>, we performed a chemical analysis using X-ray photoelectron spectroscopy. In this analysis, the Sn 3d<sub>5/2</sub> peaks (deconvoluted into 2 peaks at 484.23eV and 481.78eV corresponding to Sn<sup>4+</sup> and Sn<sup>0</sup> respectively) were chosen. By comparing the ratio of integral area under each peak, we have calculated the ratio between the 2 valence states and deduced the analysed film to be  $SnO_{1.57}$  which is similar to previous reports<sup>2</sup> regarding thermal oxidation of TDMASn with temperature lower than 150°C and using water as the oxidant. These films are shown to be a mixture of SnO and SnO<sub>2</sub> phases.

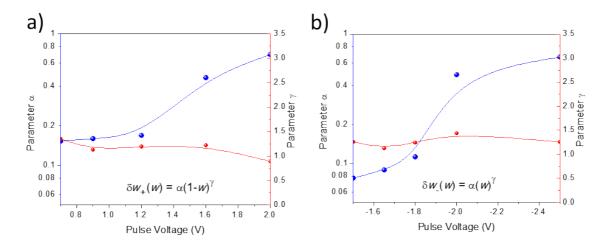

**Figure S5.** A multiplicative update scheme featuring weight-dependent rules is adopted to account for the statedependent weight modulation feature in our devices. The above graphs represent the variation in the multiplicative parameter " $\alpha$ " and state dependency factor " $\gamma$ ", indicating the soft boundaries for weight updates during (a) set and (b) reset operations.

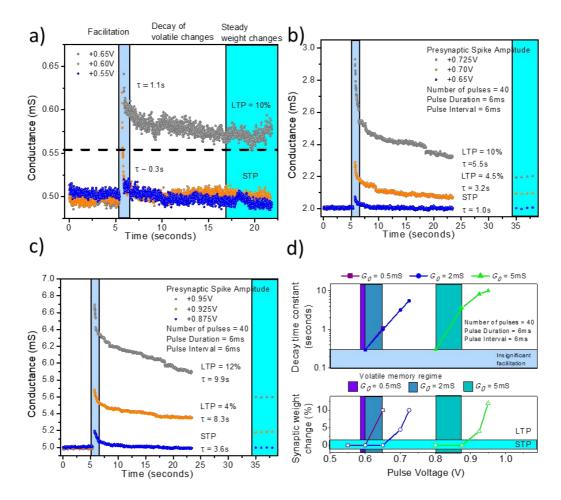

**Figure S6.** Volatile memory operation and its state dependency. Short-term potentiation and consolidation of the device conductance subjected to a pulse train of amplitude=0.5 to 0.875V, number=40 and pulse width= 6ms. Device is pre-programmed to an initial state of (a) 0.5mS, (b) 2mS and (c) 5mS. (d) The relation between the short-term memory characteristics and the pre-programmed conductance state 0.5mS, 2mS and 5mS respectively.

The devices depict a volatile or short-term memory when stimulated with small voltages. Input voltages below the LTP threshold (close to the soft boundaries of the memristor) results in temporary strengthening of EPSCs as shown in Figure S6a. Modelling the transient currents, the decay constant ' $\tau$ ' is extracted and plotted against the pulse voltages. At higher voltages (above the LTP threshold), the synaptic weight changes depict a transition from short (volatile) to long-term (non-volatile) memory. This phenomenon known as consolidation<sup>3,4</sup> is illustrated in Figure S6. Similar to the state-dependent LTP measurements<sup>5</sup>, the short-term memory characteristics also depict a dependency on the initial state of the device. To study this effect, the device is pre-programmed or initialized to 0.5mS, 2mS and 5mS states and the current transients are recorded as shown in Figures S6a-c. As evident from these figures, the volatile

memory regime is observed to lie very close to the LTP threshold at all three measured states. Figure S5d summarizes the results of Figures S6a-c, clearly depicting the variation of the decay constant ' $\tau$ ' and the threshold for consolidation with input voltage and initial conductance state.

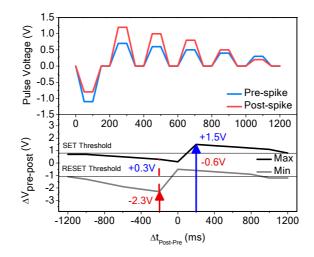

**Figure S7.** Applied STDP input pulse waveforms at the pre- and post-synaptic terminals and the effective potential difference with respect to the time delay between the pulses. A read pulse of + 0.1 V is applied at the post-synaptic terminal to read the conductance states before and after the STDP write operations.

The applied STDP waveforms are optimized in congruence with the switching characteristics of the device. The SET/RESET thresholds are established to be approximately +0.65V/-1.10V at low/high conductance states from the long-term plasticity measurements. These thresholds are indicated in Figure S7 in the plot illustrating the effective voltage developed across the device ( $\Delta V$ ) against time interval between the pre- and post-synaptic spikes ( $\Delta t$ ). The asymmetry between the SET and RESET voltages are also taken into account to accentuate the LTD side of the asymmetric Hebbian characteristics. For  $\Delta t > 0$ , where LTP is expected, the minimum  $\Delta V$  is below the RESET threshold to avoid unintended LTD effects. For example, at  $\Delta t = +200$ ms,  $V_{pre}V_{post} = (+0.70) - (-0.80) = 1.5V$  (LTP), while  $V_{min} = -0.6V$  which is below the reset threshold, hence not affecting LTP. For  $\Delta t < 0$ , where LTD is expected, the maximum  $\Delta V$  is below the SET threshold to avoid unintended LTD effects. For example, at  $\Delta t = -200$ ms  $V_{pre-}V_{post} = (-1.10) - (+1.20) = -2.3 V (LTD)$ , while  $V_{max} = +0.3V$ , which is below the set threshold, hence not affecting LTD.

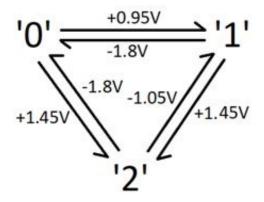

Figure S8. Modulation paths for transition between 3 states '0', '1' and '2'.

## Table S1. Comparison table for state-of-the-art multi-state memristors.

| Performance<br>parameters | Pt/TiO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub><br>/Pt<br>Sci. Rep.<br>2017, 7(1),<br>17532. | Pt/KNbO <sub>3</sub> /TiN<br>ACS Appl.<br>Mater.<br>Interfaces<br>2018, 10,<br>25673–25682 | RIR-Ir/Ta/<br>TaO <sub>2</sub> /AIO <sub>7</sub> /W<br>ACS Appl.<br>Mater.<br>Interfaces<br>2018, 10,<br>29757-29765. | TiN/ZrO <sub>2</sub> /ZrO<br>2-x/ZrO <sub>2</sub> /TiN<br>Nanoscale<br>Research<br>Letters 2017,<br>12, 384. | Ti/AlHfO,/TiN<br>Nanotechnol<br>ogy 2019, 30,<br>445205.                                            | Pt/FeOx/Pt<br>Nanotechnol<br>ogy 2018, 29,<br>495201. | Pt/a-CO <sub>x</sub> /ta-<br>C/Ag<br>Nanoscale<br>2018, 10,<br>20272. | Al/SnO,/FTO [this work]                                                                                                                  |

|---------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Size                      | Sub-µm<br>40nm TiO <sub>2</sub><br>4nm Al <sub>2</sub> O <sub>3</sub>                            | 280μm<br>diameter<br>35nm KNbO <sub>3</sub>                                                | 1-30μm<br>diameter<br>25nm TaO <sub>x</sub><br>1nm AlO <sub>y</sub>                                                   | 100μm<br>diameter<br>50nm SiN <sub>x</sub><br>1.5nm AlO <sub>y</sub>                                         | 20µm<br>crossbar<br>HfO <sub>x</sub> /AIO <sub>x</sub> /<br>HfO <sub>x</sub><br>2.5nm/1nm/<br>2.5nm | 1 – 5μm<br>crossbar<br>10nm FeO <sub>x</sub>          | 40μm<br>diameter<br>40nm a-CO <sub>x</sub>                            | 200μm diameter<br>65nm SnO <sub>x</sub>                                                                                                  |

| Dynamic<br>range          | > 3                                                                                              | > 10                                                                                       | > 100                                                                                                                 | 400                                                                                                          | < 10                                                                                                | > 10                                                  | > 2 in DC I-V<br>cycles                                               | > 10 in DC I-V<br>~ 30 with multiple pulses                                                                                              |

| Endurance<br>cycles       | No DC / AC<br>data shown                                                                         | DC - 200<br>cycles<br>(stability not<br>shown)                                             | AC - $10^{12}$<br>Cycles<br>Only for bi-<br>stable mode                                                               | DC – 100<br>Cycles<br>Only for bi-<br>stable mode                                                            | No<br>endurance<br>data shown                                                                       | AC – 100<br>pulses<br>Only for bi-<br>stable mode     | DC – 100<br>cycles<br>Only for bi-<br>stable mode                     | DC – 100 Cycles<br>>200 ternary transitions                                                                                              |

| Multi-state retention     | 8 hours for all states                                                                           | > 10 <sup>4</sup> s for all<br>5 states                                                    | > 10 <sup>4</sup> s for all<br>4 states                                                                               | Not available                                                                                                | 85ºC, 10³ s<br>for all 6<br>states                                                                  | Not available                                         | Not available                                                         | >5000s for 6 distinct programmable states                                                                                                |

| Number of<br>States       | 92 distinct<br>programmabl<br>e states with<br>low variance<br>and window<br>> 3                 | 5 distinct<br>programmabl<br>e states,<br>Programmed<br>via different<br>RESET<br>voltage  | 4 distinct<br>programmabl<br>e states                                                                                 | No distinct<br>programmabl<br>e states                                                                       | 6 distinct<br>states, in a<br>window of ~2                                                          | No distinct<br>states<br>demonstrate<br>d             | No distinct<br>states<br>demonstrate<br>d                             | 6 distinct programmable<br>states in a window of ~<br>30<br>Ternary switching with all<br>6 permutation transitions<br>in a window of ~5 |

| Forming<br>Voltage        | A series of -<br>8V to 1μs<br>pulses till 25<br>to 200 kΩ                                        | No high<br>voltage<br>forming<br>required                                                  | $5V$ for 1nm $Al_2O_3$ device                                                                                         | > 5V                                                                                                         | 4 to 5V                                                                                             | -1V, no high<br>voltage<br>forming                    | >3.5V,<br>CC=5mA                                                      | No high voltage forming required                                                                                                         |

| Compliance<br>current     | 1kΩ resistor<br>in series                                                                        | No<br>compliance<br>current for<br>multi-level<br>operation                                | No<br>compliance<br>limits<br>required                                                                                | CC=1mA for<br>SET<br>operations                                                                              | CC=0.1mA for<br>SET<br>operations                                                                   | CC=5mA for<br>SET<br>operations                       | No<br>compliance<br>limits<br>required                                | No compliance limits<br>required                                                                                                         |

#### **References:**

- Hasegawa, M. Ellingham Diagram. In *Treatise on Process Metallurgy*; Elsevier, 2014; pp 507–516.

- Mullings, M. N.; Hägglund, C.; Bent, S. F. Tin Oxide Atomic Layer Deposition from Tetrakis(Dimethylamino)Tin and Water. J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 2013, 31 (6), 061503. https://doi.org/10.1116/1.4812717.

- John, R. A.; Liu, F.; Chien, N. A.; Kulkarni, M. R.; Zhu, C.; Fu, Q.; Basu, A.; Liu, Z.;

Mathews, N. Synergistic Gating of Electro-Iono-Photoactive 2D Chalcogenide

Neuristors: Coexistence of Hebbian and Homeostatic Synaptic Metaplasticity. *Adv. Mater.* 2018, *30* (25), 1800220.

- John, R. A.; Yantara, N.; Ng, Y. F.; Narasimman, G.; Mosconi, E.; Meggiolaro, D.;

Kulkarni, M. R.; Gopalakrishnan, P. K.; Nguyen, C. A.; De Angelis, F. Ionotronic

Halide Perovskite Drift-Diffusive Synapses for Low-Power Neuromorphic

Computation. *Adv. Mater.* 2018, 1805454.

- (5) Kulkarni, M. R.; John, R. A.; Tiwari, N.; Nirmal, A.; Ng, S. E.; Nguyen, A. C.; Mathews, N. Field-Driven Athermal Activation of Amorphous Metal Oxide Semiconductors for Flexible Programmable Logic Circuits and Neuromorphic Electronics. *Small* **2019**, 1901457.