## Vertically Stacked CVD-Grown 2D Heterostructure for Wafer-Scale Electronics

Seongchan Kim,<sup>1</sup> Young Chan Kim,<sup>1</sup> Young Jin Choi,<sup>1</sup> Hwi Je Woo,<sup>1</sup> Young Jae Song,<sup>1,2</sup> Moon Sung Kang,<sup>4</sup> Changgu Lee,<sup>1,3</sup> Jeong Ho Cho<sup>5,\*</sup>

<sup>1</sup>SKKU Advanced Institute of Nanotechnology (SAINT), <sup>2</sup>Department of Physics, <sup>3</sup>School of Mechanical Engineering, Sungkyunkwan University, Suwon, 440–746, Korea.

<sup>4</sup> Department of Chemical and Biomolecular Engineering, Sogang University, Seoul 04107, Korea. <sup>5</sup>Department of Chemical and Biomolecular Engineering, Yonsei University, Seoul 03722, Korea.

\*Corresponding author: J.H.Cho (jhcho94@yonsei.ac.kr)

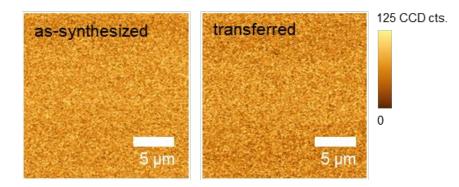

Figure S1. Raman mapping images of as-synthesized and transferred bulk  $MoS_2$  by  $E^{1}_{2g}$  mode frequency.

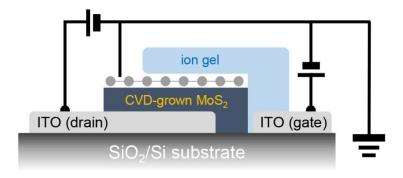

Figure S2. Cross-sectional schematic structure of the vertical transistor.

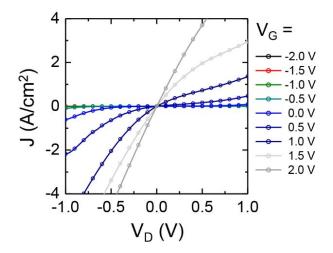

Figure S3. Linear plot of output characteristics of the vertical transistors at different  $V_{\rm GS}$ .

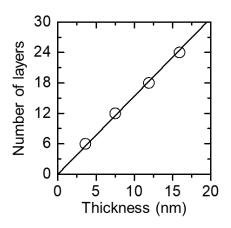

Figure S4. Number of MoS<sub>2</sub> layer as a function of the thickness.

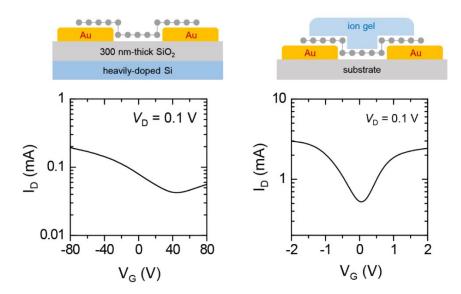

Figure S5. Transfer characteristics of the graphene transistors with the  $SiO_2$  back gate dielectrics and the ion gel top-gate dielectrics.

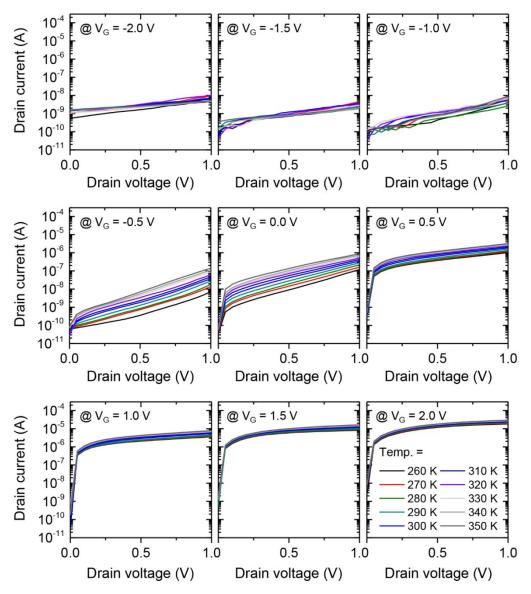

Figure S6. Output characteristics of the vertical transistors measured under various temperatures and  $V_{\rm GS}$ .

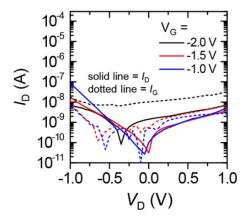

**Figure S7.**  $I_D$  and  $I_G$  as a function of  $V_D$  of the vertical transistors at  $V_G = -1.0, -1.5, \text{ and } -2.0 \text{ V}$ .