# Localized Triggering of the Insulator-Metal Transition in VO<sub>2</sub> Using a Single Carbon Nanotube

Stephanie M. Bohaichuk,<sup>1</sup> Miguel Muñoz Rojo,<sup>1,2</sup> Gregory Pitner,<sup>1</sup> Connor J. McClellan,<sup>1</sup> Feifei Lian,<sup>1</sup> Jason Li,<sup>3</sup> Jaewoo Jeong,<sup>4</sup> Mahesh G. Samant,<sup>4</sup> Stuart S. P. Parkin,<sup>4</sup> H.-S. Philip Wong,<sup>1</sup> Eric Pop<sup>1,5,\*</sup>

<sup>1</sup>Dept. of Electrical Engineering, Stanford University, Stanford, CA 94305, USA

<sup>2</sup>Dept. of Thermal and Fluid Engineering, University of Twente, 7500 AE Enschede, The Netherlands

<sup>3</sup>Asylum Research, Santa Barbara, CA 93117, USA

<sup>4</sup>IBM Almaden Research Center, San Jose, CA 95120, USA

<sup>5</sup>Dept. of Materials Science and Engineering, Stanford University, Stanford, CA 94305, USA

\*Contact: epop@stanford.edu

# **Supplementary Information Content:**

- 1. VO<sub>2</sub> Characterization and CNT Growth

- 2. Electrical Measurements of Devices

- a. Additional Electrical Characterization

- b. Semiconducting and Multi-CNT Devices

- c. Temperature Dependence

- d. Contact Resistance

- e. Series Resistance and Burn-in

- f. Switching Field

- 3. Kelvin Probe Microscopy

- 4. Three-Dimensional Finite Element Simulations

- a. Model Details

- b. Simulated Device Scaling

- c. Models Using Other Mechanisms

- 5. Supplementary Video

- 6. Supplementary References

#### 1. VO<sub>2</sub> Characterization and CNT Growth

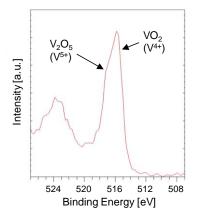

VO<sub>2</sub> thin films 9 nm thick were deposited using pulsed laser deposition on 1 cm<sup>2</sup> single crystal TiO<sub>2</sub> (101) pieces.<sup>1</sup> As-deposited VO<sub>2</sub> films were smooth with an rms roughness of ~1 Å. X-ray photoelectron spectroscopy (XPS) indicated the presence of a very thin surface oxidation, likely V<sub>2</sub>O<sub>5</sub> (Figure S1).

Separately, horizontally aligned single-wall carbon nanotubes (CNTs) were grown *via* chemical vapor deposition (CVD) on ST-cut quartz using an ethanol source, which resulted in CNTs with an average diameter of 1.2 nm.<sup>2</sup> The CNTs grew perpendicular to patterned stripes of 1.3 Å thick Fe catalyst nanoparticles, resulting in a mixture of semiconducting and metallic CNTs with a random spacing between them, on average 0.3 CNT/ $\mu$ m. This density was chosen so that fabricating 3 to 9  $\mu$ m wide VO<sub>2</sub> channels would result in a mixture of devices with no CNT, a single CNT, and multiple CNTs.

**Figure S1.** X-ray photoelectron spectroscopy (XPS) of the  $VO_2$  film prior to processing, with V2p3 peaks indicating a  $VO_2$  composition with a slight surface oxidation.

#### 2. Electrical Measurements of Devices

### 2a. Additional Electrical Characterization

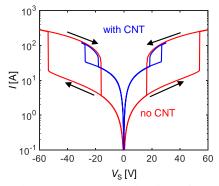

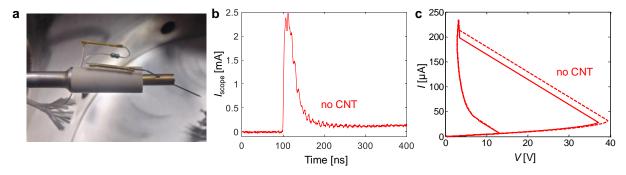

Measurements shown were all performed under vacuum (<  $10^{-4}$  Torr), removing potential effects of atmosphere or water vapour on the CNTs. However, measurements can safely be done in air and yield similar results. Figure S2 shows that devices have the same switching voltage and *I-V* characteristics regardless of bias polarity. Conduction is linear at low bias in either direction, suggesting ohmic contacts.

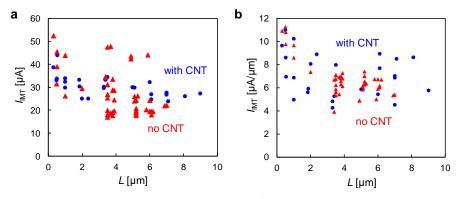

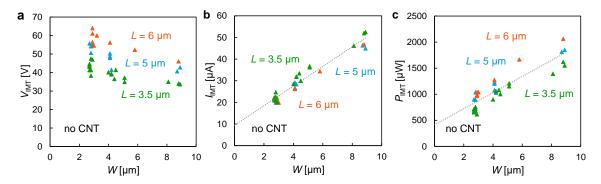

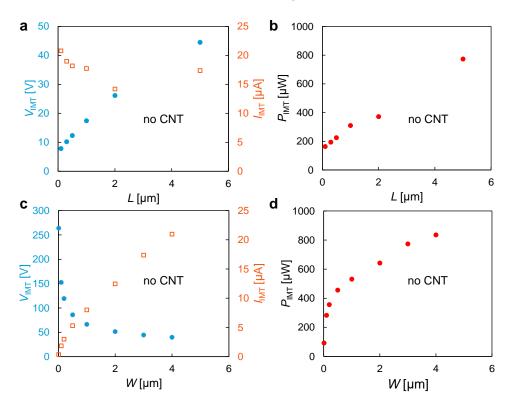

Figure S3 shows that the threshold current ( $I_{IMT}$ ) for most devices (with or without a CNT) falls roughly in the same range. For devices without a CNT, switching depends on the VO<sub>2</sub> heating that occurs throughout the entire volume. In other words, *without* a CNT the threshold current would be higher in thicker or wider VO<sub>2</sub> devices (due to larger VO<sub>2</sub> volume) and higher in shorter VO<sub>2</sub> devices (due to heat loss to the contacts). These trends can be seen in the spread of  $I_{IMT}$  for devices with VO<sub>2</sub> of different widths but without a CNT, in Figure S3a, as well as in Figure S15. However, most of our experimental devices had the same VO<sub>2</sub> thickness and nearly the same VO<sub>2</sub> widths, thus not much variation is seen in their threshold currents. In devices *with* a CNT we expect the switching current to be independent of VO<sub>2</sub> width, because the narrow CNT triggers the same heating regardless of the width of the VO<sub>2</sub> stripe underneath. The switching *voltage* of VO<sub>2</sub> devices with a CNT is lower because initially the current flows mostly in the CNT, which heats up more easily. Figure S3b shows switching current normalized by VO<sub>2</sub> width, which is appropriate for devices without a CNT but adds spread in the  $I_{IMT}$  of devices with a CNT. A slight increase in device switching voltage ( $V_{IMT}$ ) is observed in narrow devices without a CNT, as shown in Figure S4a (accompanying simulations are in Section 4b). After burn-in, which is larger for narrower devices (Section 2e),  $V_{IMT}$  has a much weaker width dependence across the range of device widths measured (3 to 9 µm). As the VO<sub>2</sub> width is reduced the switching current and power decrease slightly, shown in Figure S4b and S4c, respectively. In contrast, devices with a CNT show no dependence of  $V_{IMT}$ on VO<sub>2</sub> width, and depend solely on the CNT quality and the efficiency of heat transfer to the VO<sub>2</sub>.

**Figure S2.** Forward and reverse DC voltage-controlled switching of devices with  $(L = 6 \,\mu\text{m}, W = 2.9 \,\mu\text{m})$  and without a CNT  $(L = 6 \,\mu\text{m}, W = 5.1 \,\mu\text{m})$ , showing switching is independent of polarity.

**Figure S3.** (a) Total current just prior to switching ( $I_{IMT}$ ) for devices with (blue circles) and without (red triangles) a CNT, for a variety of widths (W = 3 to 9 µm). (b)  $I_{IMT}$  normalized by VO<sub>2</sub> width *W*, for devices with (blue circles) and without (red triangles) a CNT.

**Figure S4.** (a) Switching voltage  $V_{IMT}$  for devices without a CNT is higher in narrower devices during the first switching event. After burn-in (Section 2e),  $V_{IMT}$  shows a much weaker trend with width. (b) Switching current  $I_{IMT}$  for devices without a CNT scales linearly with width. (c) Switching power of devices without a CNT is lower in narrower devices. Dashed lines show linear fits.

#### 2b. Semiconducting and Multi-CNT Devices

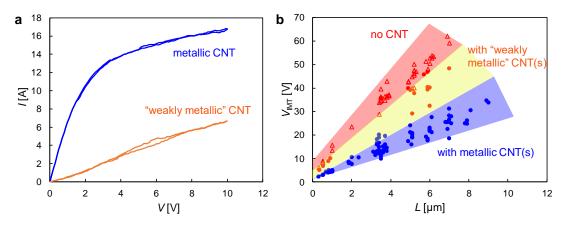

The CNT growth conditions on quartz generate a mixture of semiconducting and metallic CNTs. In addition, because the spacing between parallel CNTs is uneven, our process ultimately yields a range of VO<sub>2</sub> devices with semiconducting CNT(s), with metallic CNT(s), with a mixture of both, or with no CNTs. The presence of metallic or "weakly metallic" CNT(s) was determined by the current carried in two-terminal electrical measurements, and the number of CNTs was confirmed by atomic force microscopy (AFM). A metallic CNT carries considerably more current and will show evidence of sublinear *I-V* behaviour (typically beyond ~ 3 V when  $L \sim$  a few microns) and current saturation at higher voltages (typically near 10 to 25  $\mu$ A).<sup>3</sup> Weakly metallic CNTs (damaged or poorly contacted metallic CNTs, or CNTs with a small band gap) are less conductive and often without clear saturation. Semiconducting CNTs carry much less current (typically  $\ll 1 \ \mu$ A ungated), and their presence was verified through AFM. Examples of metallic and "weakly metallic" CNT *I-V* characteristics are shown in Figure S5a, with CNT devices fabricated in a similar manner but on TiO<sub>2</sub> (101) with no VO<sub>2</sub> film present (the substrate is insulating). Although the focus of this study was on devices with single metallic CNTs, the switching behaviours of several other types of devices were also measured. Figure S5b shows the switching voltages (V<sub>IMT</sub>) of 112 devices, including devices with CNT(s) (filled circles) and without (open triangles).

**Figure S5.** (a) Example *I-V* curves of devices  $(L \sim 4 \,\mu\text{m})$  with metallic and "weakly metallic" CNTs on TiO<sub>2</sub> (no VO<sub>2</sub> film). (b) Switching voltage  $V_{\text{IMT}}$  as a function of length (contact separation) for devices with no CNT (open triangles) and at least one CNT (filled circles). Devices with *I-V* curves that indicate the presence of metallic CNT(s) are in blue, and those without are in red. Those that show a "weakly metallic" CNT presence in their *I-V* characteristics (orange) have a switching voltage in between the two groups.

Devices with a semiconducting CNT (red circles) have the same switching voltage as devices without any CNTs (red triangles). These devices are electrically indistinguishable from each other, because the ungated semiconducting CNTs do not carry sufficiently high currents to induce heating in the  $VO_2$ .

Devices with multiple metallic CNTs switch at the same voltage as those with single metallic CNTs (both blue circles). This suggests that the transition is triggered by the "best" (*i.e.* most conductive) metallic CNT, which heats up the most. After the VO<sub>2</sub> voltage snapback (due to the series resistor  $R_S$ ) the CNTs no longer carry enough current to trigger further IMT, so any benefit to having multiple CNTs is lost. Note that all our devices have CNTs spaced far apart (~0.3 µm on average), and thus each CNT acts independently from one another. If the metallic CNTs are spaced much closer,  $V_{IMT}$  may be further reduced.

A weakly metallic CNT (orange circles) may still carry enough current to trigger IMT in the VO<sub>2</sub>, with  $V_{IMT}$  between that of a device with a good metallic CNT (blue) and one without any CNT at all (red).

#### **2c. Temperature Dependence**

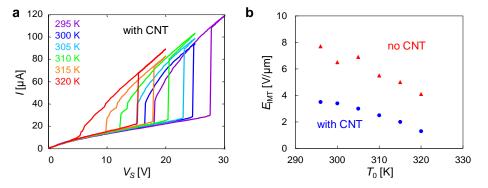

As expected,  $V_{IMT}$  reduces as the ambient temperature ( $T_0$ ) increases, which is set by the stage temperature. This is because less power is needed to raise the device temperature to  $T_{IMT}$ . This is true both for devices with (Figure S6a) and without a CNT. The switching field  $E_{IMT}$  (extracted from a linear fit to  $V_{IMT}$  vs L) decreases for both types of devices as the temperature increases, as shown in Figure S6b. If the ambient temperature is high enough (above or at  $T_{MIT}$ ), then the device will remain metallic after the bias is removed due to hysteresis in the VO<sub>2</sub>. At all temperatures, the switching field for devices with a CNT is less than half that required for devices without a CNT.  $E_{IMT}$  for a device with a CNT at 296 K is slightly below that of a device without a CNT at 320 K, suggesting that the CNT heats the VO<sub>2</sub> to at least 320 K.

**Figure S6.** (a) Switching of a device with a CNT ( $L = 5 \mu m$ ,  $W = 5.1 \mu m$ ) using DC voltage control, showing reduced switching voltage as the stage temperature increases. (b) The effective switching field  $E_{IMT}$  lowers as temperature is increased, for both devices with (blue circles) and without (red triangles) a CNT.  $E_{IMT}$  is extracted as the slope of a linear fit to  $V_{IMT}$  vs. L at each stage temperature.

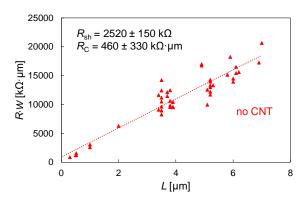

#### 2d. Contact Resistance

An estimate of the contact resistance  $R_{\rm C}$  between Pd and insulating VO<sub>2</sub> can be obtained using the transfer length method (TLM), shown in Figure S7. The y-intercept corresponds to  $2R_{\rm C}$  and the slope corresponds to the sheet resistance  $R_{\rm sh}$ . The devices are spread across the chip and have different widths, resulting in significant spread in their resistance since the cleanliness and contact quality can vary, as well as to a lesser extent the VO<sub>2</sub> resistivity and thickness. We get a value for  $R_{\rm sh}$  of  $2520 \pm 150 \text{ k}\Omega$ , and a value for  $R_{\rm C}$  of  $460 \pm 330 \text{ k}\Omega \cdot \mu \text{m}$  or equivalently, a contact resistivity  $\rho_{\rm c} \sim (0.8 \pm 0.3) \times 10^{-3} \Omega \cdot \text{cm}^2$ . For a typical 5 µm wide device, this gives a contact resistance of  $92 \pm 66 \text{ k}\Omega$ .

**Figure S7.** Insulating state resistance for VO<sub>2</sub> devices without a CNT as a function of length. The vertical axis intercept gives an estimate of twice the device contact resistance ( $2R_c$ ), and the slope gives an estimate for sheet resistance ( $R_{sh}$ ).

#### 2e. Series Resistance and Burn-in

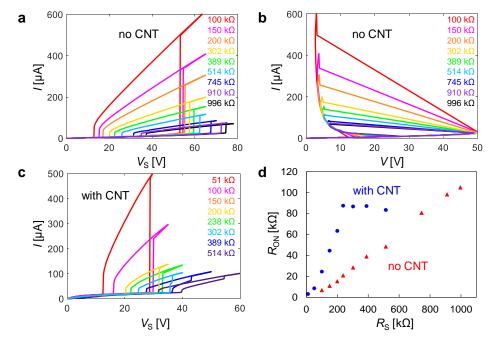

A series resistor ( $R_S$ ) is necessary to protect devices from overheating failure in the metallic state (the heat can melt the contacts). The value should be chosen low enough to not affect  $V_{IMT}$  (a small fraction of the high-resistance insulating state), but high enough to prevent permanent damage in the metallic state (higher than the low-resistance metallic state). There is no one correct value for  $R_S$  and a range of values can be used, as shown in Figure S8a. Using a larger  $R_S$  reduces the metallic state current, thus limiting the on/off ratio. There is a slight increase in the total applied voltage ( $V_S$ ) required to switch the device but  $V_{IMT}$  does not change, as shown in Figure S8b. As device dimensions are reduced, power dissipation in the metallic state reduces because  $V_{IMT}$  decreases. Thus, shorter devices do not need as high a value of  $R_S$  for protection.

Figure S8c shows that similar trends are observed for a VO<sub>2</sub> device with a CNT heater. However, when higher values of  $R_s$  are used, the transition shows an increasingly long period of slow increase in current, corresponding to oscillations, followed by a smaller abrupt transition. The CNT triggers switching in the VO<sub>2</sub>, but the subsequent reduction in voltage across the device means there is not enough power needed to remain metallic (the CNT and VO<sub>2</sub> cool) so the VO<sub>2</sub> returns to insulating, where the CNT heating is again able to switch the VO<sub>2</sub>, and the system repeatably cycles between IMT and MIT.

Figure S8d shows that as  $R_S$  increases, the metallic state resistance ( $R_{ON}$ ) of the device increases (calculated just after switching, with  $R_S$  subtracted out). This indicates that increasing  $R_S$  reduces the steady state volume of the metallic region or "filament", consistent with prior work.<sup>4</sup> As a secondary effect this change in  $R_{ON}$  could be partly due to the metallic state's temperature coefficient of resistance (TCR), since changing  $R_S$  changes the device temperature. In devices with a CNT,  $R_{ON}$  plateaus when devices show oscillatory behaviour (where  $R_{ON}$  is determined just after the final abrupt transition). This may indicate that there is a minimum width (a minimum metallic state power) required for the metallic "filament" to be stable.

Figure S9a shows where we attach the series resistor  $R_S$ , at the base of the probe tip, to avoid excess cable connections. The location of this resistor is important as well as its value. The abrupt change in device resistance triggers a large transient current due to capacitors discharging that are in parallel with the device (since I = CdV/dt).<sup>5,6</sup> This includes intrinsic device capacitance as well as other parasitic capacitances from the contacts and measurement setup such as probe pad capacitance (pad-to-pad or through the TiO<sub>2</sub> substrate to the stage) or coax cable capacitance.  $R_S$  should be physically close to the device, because then only the device capacitances see the change in conductance (the resistor shields the device from the other external capacitors). A better choice would be to use an integrated on-chip resistor (or transistor, for a variable  $R_S$  with smaller area) as a current limiter directly connected to the VO<sub>2</sub> device, however our choice in Figure S9a is the best practical one, given the setup.

A typical current overshoot event at the IMT is shown in Figure S9b for a device without a CNT, measured using a 50  $\Omega$  oscilloscope in series with the device. Although the overshoot lasts less than 100 ns, the current can transiently reach up to a few mA, which is significant compared to the few hundred  $\mu$ A which is limited by  $R_S$  when the device is in the metallic state. The overshoot duration is smaller in shorter devices. Overshoot also occurs on a similar time scale for devices with a CNT, but with a reduced magnitude.

Devices without a CNT show a burn-in effect, displayed in Figure S9c, with the first switching occurring at a slightly higher  $V_{IMT}$  than all subsequent switching. This difference is typically on the order of 0.2 - 4 V and is generally higher in narrower devices. This burn-in also results in a slight increase in insulating state conductivity. Burn-in may be a result of the heat from current overshoot at the moment of switching, which could cause a subtle change in the VO<sub>2</sub> or the contacts (such as breaking through the native surface oxide or annealing the contacts), making it slightly easier to repeat switching. Devices typically recover

from burn-in (if measured again another day then switching voltage has shifted back up for the first switching event, and the device experiences burn-in again). All other switching voltages, currents, and *I-V* characteristics reported are after this initial burn-in. Burn-in is not observed in devices with a CNT and is reduced in short devices without a CNT because of the lower switching power and current overshoot.

**Figure S8.** (a) DC voltage-controlled switching of a VO<sub>2</sub> device without a CNT ( $L = 5.1 \,\mu\text{m}$ ,  $W = 4.1 \,\mu\text{m}$ ) for different values of  $R_s$ , plotting total applied voltage  $V_s$ . (b) The same *I*-V measurements as in (a) plotted with the voltage across the device. The choice of  $R_s$  does not impact  $V_{IMT}$ . (c) DC voltage-controlled switching of a device with a CNT ( $L = 7.1 \,\mu\text{m}$ ,  $W = 2.8 \,\mu\text{m}$ ) for different  $R_s$ . (d) Device resistance just after switching ( $R_{ON}$ ), as a function of  $R_s$  for the same devices, without (red triangles) and with a CNT (blue circles).  $R_s$  can be used to control the metallic state "filament" width.

**Figure S9.** (a) Setup for using a series resistor  $R_s$  as current compliance, with  $R_s$  on the probe tip, as close as possible to the device under test. (b) Typical current overshoot when a device without a CNT switches  $(L = 3.5 \,\mu\text{m}, W = 2.7 \,\mu\text{m})$ , due to capacitive discharge. The current is measured using a 50  $\Omega$  oscilloscope in series with the device. Devices with a CNT also show current overshoot waveforms with a nearly identical shape and time-scale, but with a reduced magnitude. (c) DC voltage-controlled switching of a device without a CNT ( $L = 3.8 \,\mu\text{m}, W = 5.1 \,\mu\text{m}$ ) on the first sweep (dashed), and subsequent sweeps (solid). There is a slight shift (a "burn-in") in  $V_{\text{IMT}}$  after the first switching event.

#### 2f. Switching Field

Thermally triggered switching occurs when the steady state temperature in the device (or some part of it) reaches the insulator-metal transition temperature ( $T_{IMT}$ ). According to a very simple Joule heating description of a VO<sub>2</sub> block on a substrate, the input electrical power  $P = V^2/R$  causes the temperature to rise with a maximum determined by the thermal conductance to the surrounding environment  $G_{th}$ :

$$\frac{V^2}{R} = G_{\rm th}(T_{\rm IMT} - T_0)$$

(1)

If we write an effective switching field  $E_{IMT} = V/L$ , where V is the voltage across the VO<sub>2</sub> length L at the transition (excluding the voltage drop at the contacts), then the field could be described as:<sup>6</sup>

$$E_{\rm IMT} = \sqrt{\frac{G_{\rm th}R(T_{\rm IMT} - T_0)}{L^2}}$$

(2)

This does not capture aspects of real devices like the contacts and non-uniform heating. However, it is useful in pointing out some dependencies of the switching field. *Via*  $G_{th}$  the switching field depends on the thermal boundary resistance to the substrate, the thermal conductivity of the substrate, the geometry, and the resistivity of the VO<sub>2</sub>. Two-terminal devices can vary in this regard, making it hard to give a direct comparison of switching field. Table 1 lists switching fields of two-terminal switching devices extracted from literature with a similar change in temperature to our work ( $\Delta T = T_{IMT} - T_0 \approx 32$  K). Fields are listed as a slope (with a vertical axis intercept  $V_{offset}$  due to heat loss and resistance at the contacts) or as a long channel *V/L* where *L* is at least a few microns long. We note that thicker, wider VO<sub>2</sub> devices (lower *R*) on better thermal insulating substrates (lower *G*<sub>th</sub>) typically have lower switching field *E*<sub>IMT</sub>.

|      | Table 1. Switching Fields in Filor VO2 Films |                                     |             |       |      |          |                       |                 |            |

|------|----------------------------------------------|-------------------------------------|-------------|-------|------|----------|-----------------------|-----------------|------------|

| Ref. | Deposition                                   | Substrate                           | L           | W     | t    | Contact  | $E_{\rm IMT}$         | Voffset         | $\Delta T$ |

|      | Technique                                    |                                     | (µm)        | (µm)  | (nm) |          | (V/µm)                | (V)             | (K)        |

| 7    | PLD                                          | TiO <sub>2</sub> (001)              | 0.02 - 0.11 | 1     | 10   | Ta/Au    | 13                    | 0.1             | 35         |

| 8    | MBE                                          | TiO <sub>2</sub> (001)              | 6           | 10    | 10   | Pd/Au    | 2.2                   | -               | 35         |

| 9    | PLD                                          | SiO <sub>2</sub>                    | 2, 10       | 20    | 100  | Cr/Cu/Au | $1.2 - 4.3^{a}$       | -               | 51         |

|      |                                              | (300 nm)                            |             |       |      |          |                       |                 |            |

| 10   | sputtered                                    | SiO <sub>2</sub>                    | 0.1 - 1     | 10    | 100  | Ag, Cu,  | $2.0 - 2.3^{b}$       | $2.2 - 3.3^{b}$ | 45         |

|      | _                                            | (2 µm)                              |             |       |      | Au, Pd   |                       |                 |            |

| 11   | sputtered                                    | SiO <sub>2</sub>                    | 7.5         | 50    | 360  | Al       | 0.5                   | -               | 34         |

|      | -                                            | (500 nm)                            |             |       |      |          |                       |                 |            |

| 12   | sputtered                                    | SiO <sub>2</sub>                    | 4           | 4     | 100  | Pd/Au    | 1.2                   | -               | 28         |

|      | _                                            | (100 nm)                            |             |       |      |          |                       |                 |            |

| 13   | oxidation                                    | poly-Al <sub>2</sub> O <sub>3</sub> | 0.1 - 5     | 2, 10 | 100  | Ti/Au    | 17.4                  | 4.1             | 53         |

|      |                                              | (20 nm)                             |             |       |      |          |                       |                 |            |

| 4    | oxidation                                    | $Al_2O_3$                           | 5 - 80      | 100   | 200  | Cr/Au    | 2.9                   | 24.4            | 37         |

|      |                                              | (1120)                              |             |       |      |          | 2.2                   | 22.0            | 27         |

| 14   | PLD                                          | $Al_2O_3$                           | 5           | 50    | 90   | Cr/Au    | 2.3, 3.4 <sup>c</sup> | -               | 32         |

|      |                                              | (1102)                              |             |       |      |          |                       |                 |            |

| 15   | sputtered                                    | $Al_2O_3$                           | 20          | 100   | 100  | Ni       | 1.0                   | -               | 45         |

|      |                                              | (1010)                              |             |       |      |          |                       |                 |            |

| 16   | sputtered                                    | Al <sub>2</sub> O <sub>3</sub>      | 20          | 50    | 130  | Au       | 2.6                   | -               | 18         |

|      | _                                            | (r-cut)                             |             |       |      |          |                       |                 |            |

| 17   | sol-gel                                      | Al <sub>2</sub> O <sub>3</sub>      | 10          | 10    | 100  | Ni       | 1.0                   | -               | 45         |

Table 1. Switching Fields in Prior VO<sub>2</sub> Films

<sup>a</sup>different contact geometries, <sup>b</sup>different contact metals, <sup>c</sup>different voltage polarity

Our switching fields and intercepts fall within these ranges, although our field is on the higher end (see Figure 2c and Figure S6b, *i.e.* between ~3.5 and 7 V/µm for devices with and without a CNT, around  $T_0 = 296$  K). This is likely because our VO<sub>2</sub> films are single crystals and quite thin (higher *R*) compared to others, and because our VO<sub>2</sub> has better thermal conductance (higher  $G_{th}$ ) to the crystalline TiO<sub>2</sub> substrate.

#### 3. Kelvin Probe Microscopy (KPM)

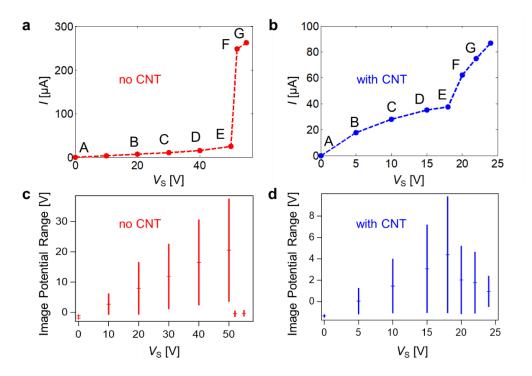

During each KPM scan the device is held at a constant voltage. The current remains constant at each bias point and is shown for the VO<sub>2</sub> device without a CNT in Figure S10a and with a CNT in Figure S10b. Because  $R_S = 200 \text{ k}\Omega$  is used, upon IMT the device voltage snaps back to ~5 V and ~8 V for devices with and without a CNT, respectively. The magnitude of the linear potential drop observed across the channel at each bias prior to flattening is shown for a device without a CNT in Figure S10c and with a CNT in Figure S10d. There is a slightly negative offset in the potential, which is determined by the workfunction difference between the tip and sample, as well as any error in the digital-to-analog converter.

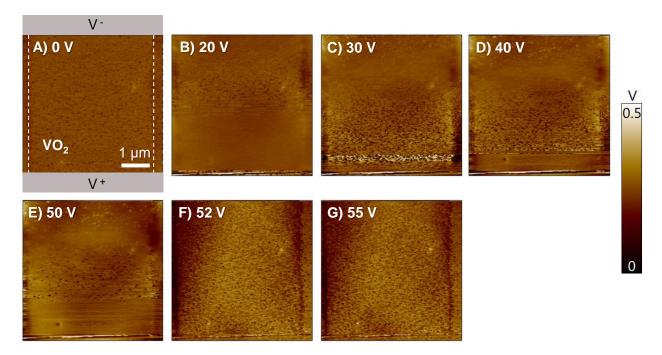

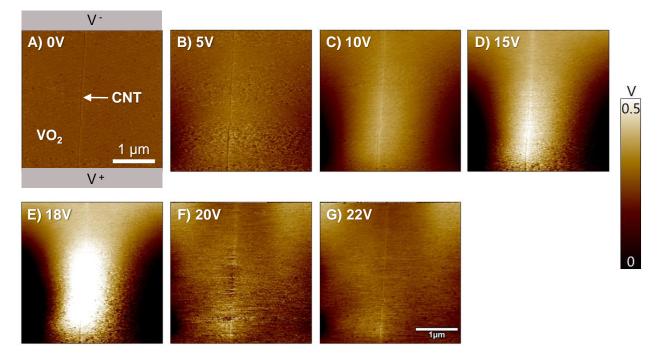

Figures S11 and S12 show the full set of KPM scans taken with increasing  $V_S$  for the devices without and with a CNT, respectively, with labels the same as in Figure S10. These images are obtained by using a first order line flattening operation, to highlight differences in surface potential across the device width. Although this CNT had a small kink, there is no additional potential drop across it, so it is not significantly more resistive and therefore not the main cause of the heating and IMT in the VO<sub>2</sub>.

**Figure S10**. Current at each applied voltage  $V_s$  during KPM measurements of devices without (a) and with a CNT (b). Raw potential drops measured across devices without (c) and with a CNT (d) prior to flattening. The potential drops after switching because of the device voltage snapback caused by  $R_s$ .

**Figure S11.** Full set of flattened KPM images of a device without a CNT. See Figure S10a for corresponding *I*-*V* data. (A) is with no bias, (B) – (E) are in the insulating state, and (F) - (G) correspond to the metallic state, with applied  $V_S$  as labeled. The electrodes are just outside the images, at the top and bottom, as labelled in (A). The edges of the VO<sub>2</sub> channel are marked in (A) with dashed lines.

**Figure S12.** Full set of flattened KPM images of a device with a CNT. See Figure S10b for corresponding *I-V* data. (A) is with no bias, (B) - (E) are in the insulating state, and (F) - (G) correspond to the metallic state, with applied  $V_S$  as labeled. The electrodes are just outside the images, at the top and bottom, as labelled in (A). The VO<sub>2</sub> channel edges are just outside the images, on the left and right.

#### 4. Three-Dimensional Finite Element Simulations

# 4a. Model Details

We developed a three-dimensional (3D) finite element model for our devices using COMSOL Multiphysics, which self-consistently considers electrical and thermal effects. An electrical model is used to calculate the voltage and current distribution in the device, while a thermal model determines the temperature distribution. These are coupled together *via* Joule heating, as well as by the temperature dependent resistivities of the CNT and VO<sub>2</sub>.

The model solves the following system of equations, where Eq. 1 is used to obtain the voltage and current distribution in the device while Fourier's law of heat conduction in steady state (Eq. 2) is used to obtain the local temperatures. *k* is the thermal conductivity, and  $\sigma$  is the electrical conductivity which is temperature dependent (and therefore spatially dependent) for the VO<sub>2</sub> and CNT. These two equations are coupled together *via J* · *E* as a Joule heating source term, with *J* being the local current density and *E* the local electric field

$$\nabla \cdot (\sigma(x, y, z, T) \nabla V) = 0 \tag{1}$$

$$\nabla \cdot (k \nabla T) + J \cdot E = 0 \tag{2}$$

For VO<sub>2</sub>, the scaling of  $\sigma$  with temperature is based on measurements of R(T) from our films as a function of stage temperature (main text Figure 1i). A room temperature  $\sigma(296 \text{ K}) = 80 \text{ S/m}$  was extracted from this data after subtracting contact resistance, and this conductivity is then scaled with temperature according to R(T)/R(296 K). The  $\sigma(T)$  data is imported as a table of temperature and resistance with ~1 K steps. When solving it is useful to use nearest-neighbour as the interpolation type, which will round the temperature of an element to the nearest table value and use the corresponding resistance. If the default linear interpolation is used then a slight change in temperature during the IMT (the steepest part of  $\sigma(T)$ ) while solving will cause a large change in resistance between solver steps, greatly hindering convergence. Only one branch (heating or cooling) of the  $\sigma(T)$  curve is used at a time for each voltage point simulated. For generating an *I-V* curve with hysteresis included, the heating branch was used as voltage was increased, and the cooling branch was used after switching as the voltage was swept back down. The solution for the previous voltage point was used as the initial conditions for the next voltage.

The conductivity of the CNT is based on a model developed by Pop *et al.*,<sup>3</sup> given by:

$$\sigma_{\rm CNT}(T,V,L) = \frac{4q^2}{h} \frac{\lambda_{\rm eff}}{A}$$

(3)

where

$$\lambda_{\text{eff}} = \left(\lambda_{\text{AC}}^{-1} + \lambda_{\text{OP,ems}}^{-1} + \lambda_{\text{OP,abs}}^{-1} + \lambda_{\text{defect}}^{-1}\right)^{-1}$$

(4)

$\lambda_{eff}$  is an effective electron mean free path (MFP) obtained using Matthiessen's rule. It combines contributions from elastic electron scattering with acoustic phonons ( $\lambda_{AC}$ ), and inelastic electron scattering by optical phonon absorption ( $\lambda_{OP,abs}$ ) and emission ( $\lambda_{OP,ems}$ ). Emission is influenced by the electric field, so this term is dependent on the applied voltage and CNT length, and all MFPs are a function of temperature. Values of  $\lambda_{OP,300} = 20$  nm and  $\hbar\omega_{OP} = 0.2$  eV are used in the model, which is described in detail in Ref. 3. An additional scattering term for defects ( $\lambda_{defect}$ ), with a mean free path of 0.8 µm, is added to better represent *I-V* characteristics of our imperfect CNTs. The reduction in CNT conductivity with increasing temperature results in current saturation behaviour of the CNT, described in Ref. 3 and seen in Figure S5a.

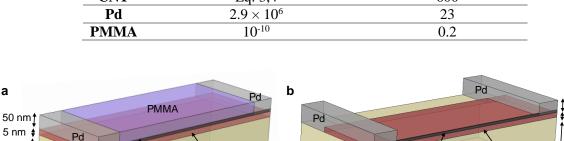

Figure S13a shows the geometry for the simulation corresponding to the device with a CNT used for SThM in main text Figure 4, and Figure S13b shows the geometry for the device simulations in main text

Figure 5. The CNT is centered in the device, so only half the device is simulated due to symmetry. The CNT is approximated as a rectangular prism 1.2 nm wide and 1.2 nm tall on top of the 5 nm thick VO<sub>2</sub>, spanning the entire length of the device and underneath the 50 nm thick Pd contacts. The simulated TiO<sub>2</sub> substrate is 2  $\mu$ m thick (unlike the ~500  $\mu$ m experimental TiO<sub>2</sub>), which is sufficient to capture its thermal resistance, most of which occurs at the thermal constriction near the CNT. For VO<sub>2</sub> devices without a CNT, where there is a significantly larger volume being heated, a 15  $\mu$ m thick TiO<sub>2</sub> substrate needs to be simulated to accurately determine the device temperature. The device for SThM is 6  $\mu$ m wide and 7  $\mu$ m long, with the VO<sub>2</sub> covered by a 50 nm thick layer of poly(methyl methacrylate) (PMMA). The other simulated VO<sub>2</sub> devices with and without a CNT are 4  $\mu$ m wide and 5  $\mu$ m long, with no PMMA capping. For these devices, a 200 kΩ series resistor  $R_S$  is modeled as a 50 nm thick resistive layer on top of one of the contacts, with a resistivity chosen to give a total resistance of 200 kΩ. The  $R_S$  layer does not thermally interact with the device. Including the extra width of TiO<sub>2</sub> beyond the VO<sub>2</sub> width makes no significant difference to devices with a CNT (whose VO<sub>2</sub> edges are near room temperature far from the CNT heating), but a large width of TiO<sub>2</sub> is needed to fully capture the thermal profile in devices without a CNT. Material parameters are listed in Table 2.

The top of one contact is grounded, and the top of the other (or the top of  $R_s$ , if applicable) is set at a constant potential. Electrical contact resistance is simulated on internal boundaries between CNT/Pd (25 k $\Omega$ ), CNT/VO<sub>2</sub> (100 k $\Omega$ ) and VO<sub>2</sub>/Pd. The VO<sub>2</sub>/Pd contact resistivity is set to  $0.8 \times 10^{-3} \Omega \cdot cm^2$  (see Section 2d) at room temperature and scaled with temperature in the same way as the VO<sub>2</sub> resistivity (by using the heating branch of R(T)/R(296 K) for the forward voltage sweep and the cooling branch of R(T)/R(296 K) for the boundaries are modeled as electrically insulating.

The bottom of the TiO<sub>2</sub> is fixed at room temperature (296 K). The top of the device is assumed to be thermally insulating (adiabatic), and the sides of the device have open boundary conditions. The Pd resistivity is taken from measurements of our films, and its thermal conductivity is estimated from the Wiedemann-Franz law. Thermal boundary resistance (TBR) is simulated on all interior boundaries. These interfacial resistances cannot be ignored, since they limit the flow of heat (especially from the CNT to the VO<sub>2</sub> but also from the VO<sub>2</sub> to the TiO<sub>2</sub> substrate), impacting the local VO<sub>2</sub> temperature and therefore the switching voltage. The CNT/VO<sub>2</sub> interface is set to  $5 \times 10^{-9} \text{ m}^2 \text{K/W}$ , the TiO<sub>2</sub>/VO<sub>2</sub> interface to  $8 \times 10^{-9} \text{ m}^2 \text{K/W}$ , and all other interfaces to  $10^{-8} \text{ m}^2 \text{K/W}$ . To the authors' knowledge these have not been experimentally measured, so were adjusted within reason<sup>19</sup> to better fit the *I-V* characteristics of the VO<sub>2</sub> device with a CNT used for SThM in main text Figure 4e.

All simulations were solved with a segregated approach, which solves each physics (temperature and voltage) sequentially, repeating until convergence is achieved. The matrix equation containing the description of the physics (Eq. 1 or 2) on each mesh element is solved using a direct approach (as opposed to iterative) with the MUMPS solver. The temperature was solved as the first step, followed by the electric potential. To help with convergence when solving across the IMT, the electric potential step was given two iterations instead of the default one (the solver will solve temperature, electric field, electric field again, temperature, *etc.* repeating until convergence). To also help simulate the IMT, the damping factors were set to 0.1 and 0.4 for the temperature and potential segregated steps respectively. The damping factor is a scaling factor reducing the size of the step taken at each iteration of the physics (rather than using the current step's solution as the next starting point, which would correspond to a damping factor of 1). If these factors are not reduced, then the solver will overshoot the solution and oscillate between insulating and completely metallic (the entire device width switched, with too much heat and current), since the problem is nonlinear.

| Table 2. Material properties used in simulation |                                        |                                       |  |  |  |

|-------------------------------------------------|----------------------------------------|---------------------------------------|--|--|--|

|                                                 | σ [S/m]                                | k [Wm <sup>-1</sup> K <sup>-1</sup> ] |  |  |  |

| TiO <sub>2</sub>                                | 10-7                                   | 8                                     |  |  |  |

| VO <sub>2</sub>                                 | function of $T(x,y,z)$ spanning        | 5                                     |  |  |  |

|                                                 | 80 to $2 \times 10^6$ (see Section 4a) |                                       |  |  |  |

| CNT                                             | Eq. 3,4                                | 600                                   |  |  |  |

| Pd                                              | $2.9 	imes 10^6$                       | 23                                    |  |  |  |

| PMMA                                            | 10-10                                  | 0.2                                   |  |  |  |

а

5 nm

2 µm

VO2

CNT

TiO

Figure S13. (a) Half-device structure used to simulate the experimental device used for SThM in main Figure 4. (b) Half-device structure used to simulate switching and full *I-V* curves in main Figure 5. For the device without a CNT a larger TiO<sub>2</sub> substrate is used, with dimensions indicated in brackets.

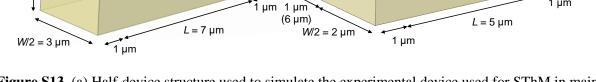

Simulated temperatures on the surface of a  $VO_2$  device without a CNT are shown just before (Figure S14a) and just after (Figure S14b) IMT, corresponding to the simulated *I-V* curve in main text Figure 5c. Before switching there is significant bulk Joule heating, and the device requires much more power for switching than with a CNT. A ~400 nm wide metallic "filament" is formed upon IMT in the center of the  $VO_2$  device, much wider than the ~10 nm wide "filament" in the device with a CNT. In practical devices, the filament is likely larger due to transient current overshoot, caused by parasitic capacitors discharging at the moment of switching, combined with hysteresis.

**Figure S14.** Simulated temperature on the surface of a VO<sub>2</sub> device without a CNT ( $L = 5 \mu m$ ,  $W = 4 \mu m$ ) just before (a) and just after (b) the metallic transition, with  $R_{\rm S} = 200 \text{ k}\Omega$ . VO<sub>2</sub> requires a higher switching power than devices with a CNT because it relies on bulk Joule heating. After switching, a metallic region forms in the center of the device, where it is hottest, with its size determined by current overshoot and  $R_{\rm S}$ . The color scalebar in (b) is cut off at  $T_{IMT} = 328$  K to highlight the switching region as dark red, though the temperature in the center of the metallic VO<sub>2</sub> region is higher.

50 nm

5 nm

2 µm

(15 µm)

VO2

CNT

TiO

1 µm

#### 4b. Simulated Device Scaling

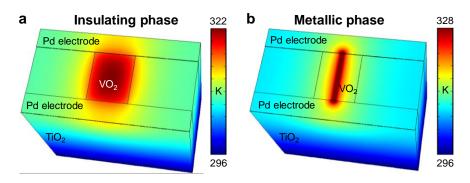

Simulated switching voltage  $V_{IMT}$ , current  $I_{IMT}$ , and power  $P_{IMT}$  of VO<sub>2</sub> devices without a CNT are shown in Figure S15 for a variety of device lengths and widths. As device length is reduced (Figure S15a-b), both  $P_{IMT}$  and  $V_{IMT}$  decrease nearly linearly.  $I_{IMT}$  has little length dependence, with only a slight increase in very short devices. These scaling trends match well with what is seen experimentally (Figure 2c-d and Figure S3-4) and reaffirm the thermal dependence of electrical switching in VO<sub>2</sub>.

As device width is reduced (Figure S15c-d), contact resistance increases and  $V_{IMT}$  increases steeply below ~ 1 µm. However,  $I_{IMT}$  also decreases, resulting in a net decrease in  $P_{IMT}$  for narrower devices. In contrast, VO<sub>2</sub> devices with a CNT have no width dependence on switching characteristics. Given these trends, adding a CNT to an ultra-narrow VO<sub>2</sub> device would have the benefit of maintaining a much lower, width-independent switching voltage (see Table 3 for a simulated example). However, because the CNT is more conductive than an ultra-narrow stripe of VO<sub>2</sub>, this comes at the cost of increased insulating state current and therefore reduced on/off ratio. This could result in little improvement in overall switching power, if any. To retain access to a higher resistance state with low current, a gateable semiconducting CNT or other nonlinear heat source (*e.g.* nanowire, diode, switching material, *etc.*) could be used instead.

**Figure S15.** Simulated scaling trends of VO<sub>2</sub> devices without a CNT, with thermally induced switching. (a) Switching voltage  $V_{IMT}$  (solid blue circles) decreases with device length (simulated down to 100 nm length, with  $W = 5 \mu m$ ) and switching current  $I_{IMT}$  (hollow orange squares) starts to increase slightly below ~ 1  $\mu m$ . (b) Total device power  $P_{IMT}$  reduces linearly with length. (c) In narrow devices (simulated down to 10 nm width),  $V_{IMT}$  is much higher but  $I_{IMT}$  decreases ( $L = 5 \mu m$ ). (d) Switching power decreases as device width is reduced ( $L = 5 \mu m$ ).

| witching of Narrow Devices | $s(L-3 \mu m, w - 100 mm)$ |

|----------------------------|----------------------------|

| without CNT                | with CNT                   |

| 153                        | 9                          |

| 2                          | 33                         |

| 282                        | 528                        |

|                            | without CNT                |

**Table 3.** Simulated Switching of Narrow Devices ( $L = 5 \mu m$ , W = 100 nm)

**Table 3.** Simulated switching of long, narrow  $VO_2$  devices with and without a CNT. The CNT greatly reduces the switching voltage but comes with a higher switching current and power (although the simulated CNT is more conductive than imperfect experimental CNTs). By also reducing the device length, the switching voltage and power would decrease for both types of devices.

In thermally triggered devices, there is a trade-off between low switching voltage and current because enough total power is still required to reach the transition temperature. The addition of an extra Joule heating source with an appropriate current density can shift device operation to a lower switching voltage instead of low current. Some additional control over switching voltage could be achieved by engineering the thermal environment of the device, for example, by changing the thermal boundary resistance to and the thermal conductivity of the substrate to reduce heat loss from the VO<sub>2</sub>. If this improves heating efficiency (*e.g.* by confining heating to a small volume), then a lower switching power can be achieved.

These simulated scaling trends are estimates, assuming similar electrical and thermal transport at small length scales. In reality, there may be some differences when devices are shrunk to the nanoscale. For example, thermal and electrical conductivity of the  $VO_2$  may decrease when narrower (due to surface boundary scattering), which could affect the switching trends.

# 4c. Models Using Other Mechanisms

We note that there are two fields at play in the devices with CNTs: the lateral field between source and drain electrodes, corresponding to  $E_{IMT}$  in Figure S6b, and the vertical field emitted by the ultra-narrow CNT into the VO<sub>2</sub> below. A simple simulation involving the vertical field is very difficult, without knowing *e.g.* the band alignment at their interface. Therefore, we have focused on two types of simulations involving only the lateral field. In both of these, Joule heating cannot be neglected and still plays a large role, but the fundamental switching mechanism is field-driven. VO<sub>2</sub> devices can still show switching behaviour similar to experiment, with a reduction in switching voltage seen in the devices with a CNT. Although there can be slight changes in the local field with the addition of a CNT, the reduction in switching voltage is primarily due to the heating generated by the CNT, though the increased temperature could be directly driving the transition, lowering the required field, or increasing the carrier concentration in the VO<sub>2</sub>.

In the first model, Joule heating reduces the critical field  $E_{crit}$  required for VO<sub>2</sub> switching. We use a linear fit to data from devices without a CNT in Figure S6b, shown in Eq. (5) in units of V/µm, with *T* being temperature in Kelvin, and a = -0.14 V/µm/K and b = 49 V/µm are fitting constants:

$$E_{\rm crit} = aT + b \tag{5}$$

We note that very close to  $T_{IMT}$ , the temperature dependence of  $E_{crit}$  may not be linear, because it is expected that  $E_{crit}$  should approach zero at  $T_{IMT}$ . An alternative expression could be fitted to the data in Figure S6b:

$$E_{\rm crit} = E_0 \sqrt{1 + T/T_{IMT}} \tag{6}$$

where  $E_0 = 25 \text{ V/}\mu\text{m}$  is a fitting constant. If switching happens considerably below  $T_{\text{IMT}}$  in the model, then the difference between Eq. (5) and (6) is found to have very little impact on switching behaviour. However, the use of Eq. (6) ensures that the device will switch at  $T \le T_{\text{IMT}}$ , especially in devices with a CNT where there is significant heating. The temperature dependence of the insulating state electrical conductivity of the VO<sub>2</sub> follows Eq. (7), fit with an activation energy  $E_a = 0.21$  eV and a constant  $\sigma_0 = 3 \times 10^5$  S/m to our R(T) data (main text Figure 1i). T is the temperature in Kelvin, and  $k_{\text{B}} = 8.617 \times 10^{-5}$  eV/K is the Boltzmann constant. The VO<sub>2</sub> conductivity increases abruptly to metallic ( $\sigma = 2 \times 10^5$  S/m) once  $E_{\text{crit}}$  is reached. The contact resistivity of the VO<sub>2</sub> to the Pd is scaled with the VO<sub>2</sub> conductivity, similar to our other simulations.

$$\sigma = \sigma_0 \exp\left(-\frac{E_a}{k_{\rm B}T}\right) \tag{7}$$

In the second model, electrical conductivity in the insulating state follows a 3D Poole-Frenkel transport model<sup>20</sup> according to Eq. (8), dependent on both the electric field *E* and the temperature *T* in the device.  $\sigma_0$  and  $E_a$  were fit to experimental *I-V* data giving  $9 \times 10^3$  A/m<sup>2</sup> and 0.22 eV respectively. A relative dielectric constant  $\varepsilon_r = 38$  was used<sup>21</sup> for VO<sub>2</sub> to calculate  $\beta$  using Eq. (9). Conductivity can be converted to a carrier concentration  $n = \sigma E/(q\mu)$  using a mobility<sup>22</sup>  $\mu = 0.5$  cm<sup>2</sup>/V/s. This is compared to a critical carrier concentration  $n_c = 1.5 \times 10^{19}$  cm<sup>-3</sup> estimated from the Mott criteria for an IMT, consistent with Hall measurements of the carrier concentration at the transition point.<sup>22</sup> Once the carrier concentration exceeds  $n_c$ , the VO<sub>2</sub> becomes metallic ( $\sigma = 2 \times 10^5$  S/m). Again, the contact resistivity of the VO<sub>2</sub> to the Pd is scaled with the VO<sub>2</sub> conductivity, similar to our other simulations.

$$\sigma = \frac{\sigma_0}{E} \exp\left(-\frac{E_a}{2k_{\rm B}T}\right) \left[ \left(\frac{k_{\rm B}T}{\beta}\right)^2 \left(1 + \left(\frac{\beta\sqrt{E}}{2k_{\rm B}T} - 1\right) \exp\left(\frac{\beta\sqrt{E}}{2k_{\rm B}T}\right) \right) + \frac{E}{2} \right]$$

(8)

$$\beta = \sqrt{\frac{q^3}{\pi\epsilon_r\epsilon_0}} \tag{9}$$

Geometry, thermal conductivities, thermal boundary resistance, and the CNT electrical conductivity is kept the same as in our thermally-driven simulation (see Section 4a). The  $\sigma(T,E)$  data is imported as a table of local temperature, field, and resistance with ~1 K steps. When solving it is best to avoid using nearest-neighbour as the interpolation type, which will produce artifacts in the local field. Because of the stronger coupling of the field to conductivity, the problem becomes increasingly nonlinear. This makes it very challenging to reach convergence in the metallic state, so we have only simulated up to the IMT.

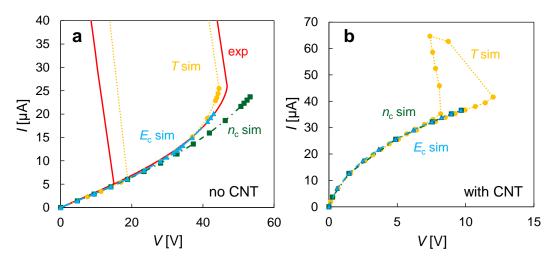

In the temperature-dependent electric field model using Eq. (5) to (7), the switching voltage of a device without a CNT is ~34 V, considerably lower than experiments and other models shown in Figure S16. Switching occurs at a much lower temperature (~ 315 K) than  $T_{IMT}$ . In devices with a CNT, the switching voltage is reduced to ~11 V and the VO<sub>2</sub> temperature reaches ~ $T_{IMT}$  underneath the CNT. Increasing thermal properties within reason for devices without a CNT in order to reduce the VO<sub>2</sub> temperature ( $k_{TiO2} = 15$  Wm<sup>-1</sup>K<sup>-1</sup>,  $k_{VO2} = 7$  Wm<sup>-1</sup>K<sup>-1</sup>, and a TiO<sub>2</sub>/VO<sub>2</sub> interface TBR = 5×10<sup>-9</sup> m<sup>2</sup>K/W) only slightly raises the switching voltage by ~2 V and *cannot* reproduce the experimental switching voltage. However, it is likely that  $E_{crit}$  at a given temperature is higher than that given by fits to Figure S6b, since the local device temperature is higher than the ambient temperature. Increasing the required field at a given temperature by setting b = 54 V/µm in Eq. (5) or  $E_0 = 40$  V/µm in Eq. (6), and using the original thermal properties in Table 2, fits experimental data for devices without a CNT much more closely, shown as " $E_c$  sim" in Figure S16. When Eq. (6) with  $E_0 = 40$  V/µm is used to simulate devices with a CNT, the switching voltage remains ~10 V even with the higher required field, because switching is set more by the VO<sub>2</sub> reaching  $T ~ T_{IMT}$  (where  $E_{crit} ~ 0$ ) than by changes in the local field induced by the CNT.

Both field-based models can then produce electrical switching behaviour similar to experiment, shown in Figure S16 for devices with and without a CNT. Thus, we cannot rule out a thermally-assisted transition based on reaching a critical field or carrier concentration, rather than just a critical temperature. All models show a similar reduction in switching voltage for devices with a CNT when compared to  $VO_2$  devices without a CNT, due to the heating of the  $VO_2$  by the CNT.

**Figure S16.** Simulated voltage-controlled *I*-*V* curves for VO<sub>2</sub> devices without (a) and with (b) a CNT ( $L = 5 \mu m$ ,  $W = 4 \mu m$  for the VO<sub>2</sub>). Several models are used: a model where the IMT depends only on temperature (labelled "*T* sim", orange dots), a model where IMT is triggered by a temperature-dependent critical electric field (labelled " $E_c$  sim", blue dashes and triangles), and a model where IMT is triggered by a critical carrier concentration dependent on temperature and electric field (labelled " $n_c$  sim", dark green dot-dashes and squares). In models with a field dependence, the last data point shown is just before IMT.

#### **5. Supplementary Video**

Video S1 (uploaded separately) shows the evolution of surface temperature of the simulated device with a CNT (main Figure 5a), as the voltage is swept up and then down on the *I*-*V* curve (main Figure 5b).

# **6. Supplementary References**

- Jeong, J.; Aetukuri, N.; Graf, T.; Schladt, T. D.; Samant, M. G.; Parkin, S. S., Suppression of Metal-Insulator Transition in VO<sub>2</sub> by Electric Field-Induced Oxygen Vacancy Formation. *Science* 2013, *339*, 1402-1405.

- Patil, N.; Lin, A.; Myers, E. R.; Koungmin, R.; Badmaev, A.; Chongwu, Z.; Wong, H. S. P.; Mitra, S., Wafer-Scale Growth and Transfer of Aligned Single-Walled Carbon Nanotubes. *IEEE Trans. Nanotechnol.* 2009, *8*, 498-504.

- 3. Pop, E.; Mann, D. A.; Goodson, K. E.; Dai, H., Electrical and Thermal Transport in Metallic Single-Wall Carbon Nanotubes on Insulating Substrates. *J. Appl. Phys.* **2007**, *101*, 093710.

- 4. Yoon, J.; Lee, G.; Park, C.; Mun, B. S.; Ju, H., Investigation of Length-Dependent Characteristics of the Voltage-Induced Metal Insulator Transition in VO<sub>2</sub> Film Devices. *Appl. Phys. Lett.* **2014**, *105*, 083503.

- Wan, H. J.; Zhou, P.; Ye, L.; Lin, Y. Y.; Tang, T. A.; Wu, H. M.; Chi, M. H., *In Situ* Observation of Compliance-Current Overshoot and Its Effect on Resistive Switching. *IEEE Electron Device Lett.* 2010, *31*, 246-248.

- 6. Yu, S.; Guan, X.; Wong, H.-S. P., Understanding Metal Oxide RRAM Current Overshoot and Reliability Using Kinetic Monte Carlo Simulation. *IEEE Int. Electron Devices Meet.* 2012.

- 7. Aetukuri, N. P. B. The Control of Metal-Insulator Transition in Vanadium Dioxide. Ph.D. Thesis, Stanford University, 2013, https://searchworks.stanford.edu/view/10163818.

- Li, D.; Sharma, A. A.; Gala, D. K.; Shukla, N.; Paik, H.; Datta, S.; Schlom, D. G.; Bain, J. A.; Skowronski, M., Joule Heating-Induced Metal-Insulator Transition in Epitaxial VO<sub>2</sub>/TiO<sub>2</sub> Devices. *ACS Appl. Mater. Interfaces* 2016, *8*, 12908-12914.

- 9. Vitale, W. A.; Tamagnone, M.; Moldovan, C. F.; Emond, N.; Casu, E. A.; Petit, L.; Le Drogoff, B.; Chaker, M.; Mosig, J. R.; Ionescu, A. M., Field-Enhanced Design of Steep-Slope VO<sub>2</sub> Switches for Low Actuation Voltage. *Proc. Eur. Solid-State Device Res. Conf.* **2016**.

- Joushaghani, A.; Jeong, J.; Paradis, S.; Alain, D.; Stewart Aitchison, J.; Poon, J. K. S., Voltage-Controlled Switching and Thermal Effects in VO<sub>2</sub> Nano-Gap Junctions. *Appl. Phys. Lett.* 2014, 104, 221904.

- 11. Vitale, W. A.; Moldovan, C. F.; Tamagnone, M.; Paone, A.; Schuler, A.; Ionescu, A. M., Steep-Slope Metal-Insulator-Transition VO<sub>2</sub> Switches with Temperature-Stable High I<sub>ON</sub>. *IEEE Electron Device Lett.* **2015**, *36*, 972-973.

- Madan, H.; Jerry, M.; Pogrebnyakov, A.; Mayer, T.; Datta, S., Quantitative Mapping of Phase Coexistence in Mott-Peierls Insulator during Electronic and Thermally Driven Phase Transition. ACS Nano 2015, 9, 2009-2017.

- Radu, I. P.; Govoreanu, B.; Mertens, S.; Shi, X.; Cantoro, M.; Schaekers, M.; Jurczak, M.; De Gendt, S.; Stesmans, A.; Kittl, J. A.; Heyns, M.; Martens, K., Switching Mechanism in Two-Terminal Vanadium Dioxide Devices. *Nanotechnology* 2015, *26*, 165202.

- 14. Kim, H.-T.; Chae, B.-G.; Youn, D.-H.; Kim, G.; Kang, K.-Y.; Lee, S.-J.; Kim, K.; Lim, Y.-S., Raman Study of Electric-Field-Induced First-Order Metal-Insulator Transition in VO<sub>2</sub>-Based Devices. *Appl. Phys. Lett.* **2005**, *86*, 242101.

- 15. Kim, B.-J.; Lee, Y. W.; Choi, S.; Yun, S. J.; Kim, H.-T., VO<sub>2</sub> Thin-Film Varistor Based on Metal-Insulator Transition. *IEEE Electron Device Lett.* **2010**, *31*, 14-16.

- Zimmers, A.; Aigouy, L.; Mortier, M.; Sharoni, A.; Wang, S.; West, K. G.; Ramirez, J. G.; Schuller, I. K., Role of Thermal Heating on the Voltage Induced Insulator-Metal Transition in VO<sub>2</sub>. *Phys. Rev. Lett.* 2013, *110*, 056601.

- Kim, H.-T.; Kim, B.-J.; Choi, S.; Chae, B.-G.; Lee, Y. W.; Driscoll, T.; Qazilbash, M. M.; Basov, D. N., Electrical Oscillations Induced by the Metal-Insulator Transition in VO<sub>2</sub>. *J. Appl. Physs* 2010, *107*, 023702.

- Martens, K.; Radu, I. P.; Mertens, S.; Shi, X.; Nyns, L.; Cosemans, S.; Favia, P.; Bender, H.; Conard, T.; Schaekers, M.; De Gendt, S.; Afanas'ev, V.; Kittl, J. A.; Heyns, M.; Jurczak, M., The VO<sub>2</sub> Interface, the Metal-Insulator Transition Tunnel Junction, and the Metal-Insulator Transition Switch On-Off Resistance. J. Appl. Phys. 2012, 112, 124501.

- 19. Pop, E., Energy Dissipation and Transport in Nanoscale Devices. *Nano Res.* 2010, *3*, 147-169.

- 20. Gibson, G. A.; Musunuru, S.; Zhang, J.; Vandenberghe, K.; Lee, J.; Hsieh, C.-C.; Jackson, W.; Jeon, Y.; Henze, D.; Li, Z.; Williams, R. S., An Accurate Locally Active Memristor Model for S-Type Negative Differential Resistance in NbO<sub>x</sub>. *Appl. Phys. Lett.* **2016**, *108*, 023505.

- 21. Yang, Z.; Ko, C.; Balakrishnan, V.; Gopalakrishnan, G.; Ramanathan, S., Dielectric and Carrier Transport Properties of Vanadium Dioxide Thin Films across the Phase Transition Utilizing Gated Capacitor Devices. *Phys. Rev. B* **2010**, *82*, 205101.

- 22. Ruzmetov, D.; Heiman, D.; Claflin, B. B.; Narayanamurti, V.; Ramanathan, S., Hall Carrier Density and Magnetoresistance Measurements in Thin-Film Vanadium Dioxide across the Metal-Insulator Transition. *Phys. Rev. B* **2009**, *79*, 153107.