## **Supporting Information**

Gate-Tunable and Programmable n-InGaAs/Black

Phosphorus Heterojunction Diodes

Youngsu Lee<sup>†</sup>, Doo-Seung Um<sup>†</sup>, Seongdong Lim<sup>†</sup>, Hochan Lee<sup>†</sup>, Minsoo P. Kim<sup>†</sup>, Tzu-Yi

Yang<sup>‡</sup>, Yu-Lun Chueh<sup>‡</sup>, Hyung-jun Kim<sup>§</sup> and Hyunhyub Ko<sup>\*†</sup>

†School of Energy and Chemical Engineering, Ulsan National Institute of Science and

Technology (UNIST), Ulsan Metropolitan City, 44919, Republic of Korea

<sup>‡</sup>Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu,

30013, Taiwan, Republic of China

State Key Laboratory of Advanced Processing and Recycling of Non-ferrous Metals, Lanzhou

University of Technology, School of Materials Science and Engineering, Lanzhou University

of Technology, Lanzhou 730050, PR China

§Center for Spintronics, Korea Institute of Science and Technology (KIST), Seoul 02792,

Republic of Korea

\*E-mail: hyunhko@unist.ac.kr

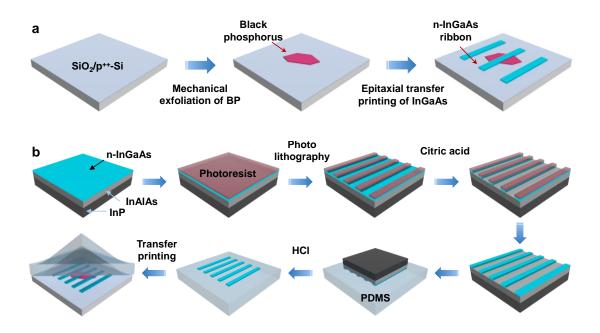

**Figure S1.** (a) Schematic of the fabrication process of n-InGaAs-BP heterojunction diode. (b) Schematic illustration of details of patterning and transfer printing process of n-InGaAs nanomembrane.

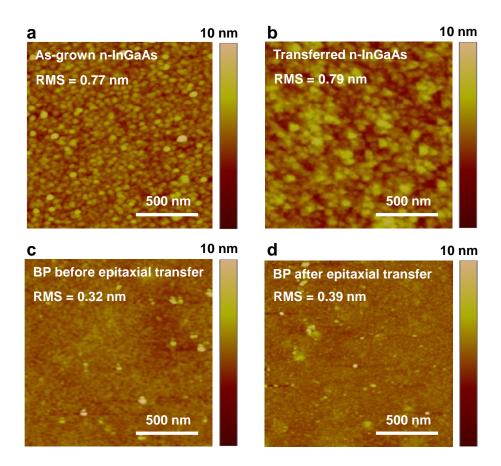

**Figure S2**. AFM images for the surface roughness of (a) as-grown n-InGaAs and (b) transferred n-InGaAs. AFM images for the surface roughness of BP (a) before the epitaxial transfer printing process of n-InGaAs and (d) after the epitaxial transfer printing process of n-InGaAs.

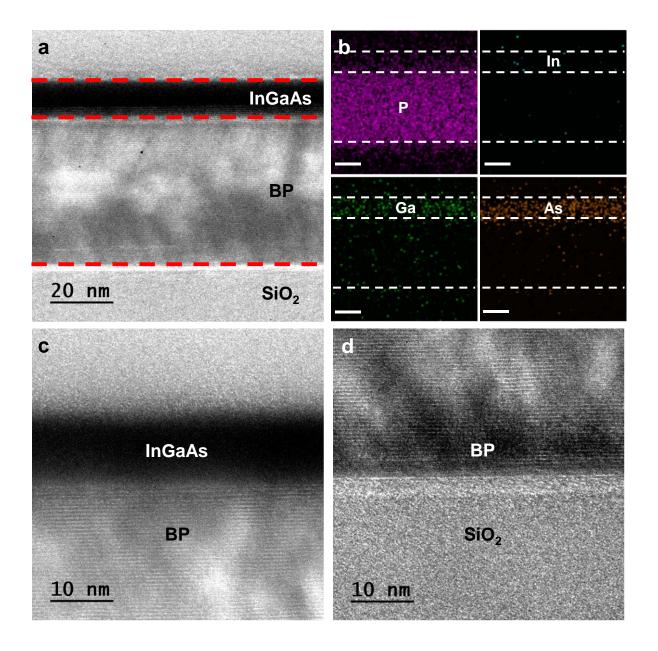

**Figure S3.** (a) Cross-sectional HRTEM image of n-InGaAs and BP heterojunction. (b) EDS elemental mappings of phosphorus (P), Indium (In), Gallium (Ga), Arsenic (As) of n-InGaAs and BP heterojunction. Scale bar is 10 nm. (c) and (d) Cross-sectional HRTEM images of the interface of (c) InGaAs/BP and (d) BP/SiO<sub>2</sub>.

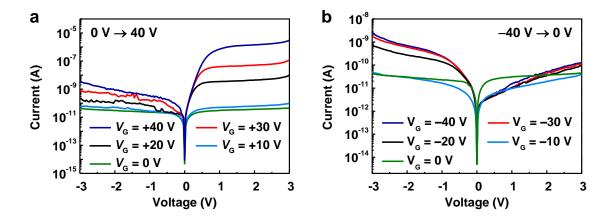

**Figure S4.** *I-V* characteristics of n-InGaAs–BP heterojunction diode under different gate voltages (a) from 0 to 40 V and (b) from –40 to 0 V.

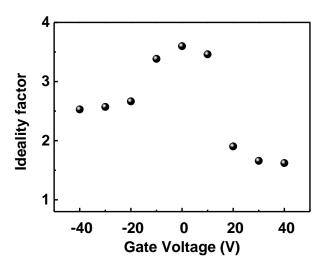

Figure S5. Estimated ideality factor as a function of gate voltages.

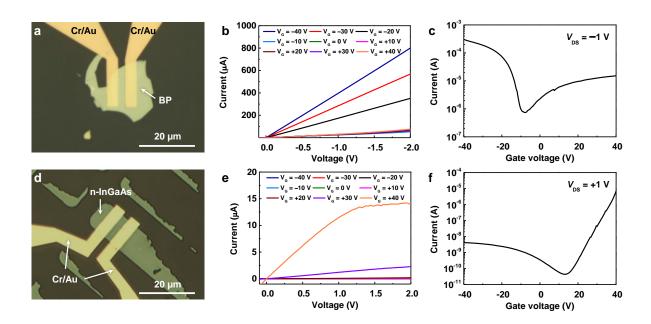

**Figure S6.** (a) Optical-microscope image and (b) output characteristics of BP FET. (c) Transfer characteristics of BP FET at  $V_{DS} = -1$  V. (d) Optical image and (e) output characteristics of n-InGaAs FET. (f) Transfer characteristics of n-InGaAs FET at  $V_{DS} = 1$  V.

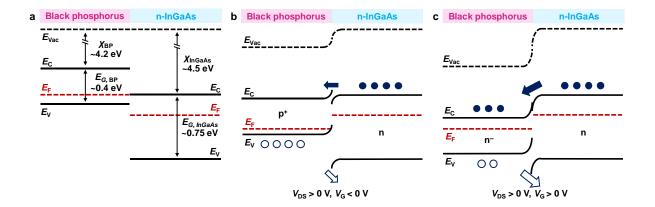

**Figure S7.** (a) Schematic illustration of estimated band alignment between BP and n-InGaAs. Schematic energy-band diagrams of heterojunction diode under forward bias with (b) negative gate voltage and (c) positive gate voltage.  $E_{\text{Vac}}$ ,  $E_{\text{C}}$ ,  $E_{\text{V}}$ ,  $E_{\text{F}}$ ,  $E_{\text{G}}$  and  $\chi$  are the vacuum level, lowest energy level of the conduction band, the highest energy level of the valence band, the Fermi level, the band gap and the electron affinity of the semiconductors, respectively.

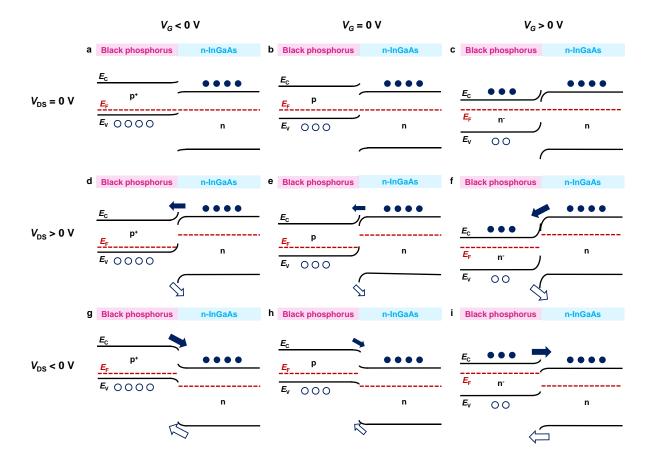

**Figure S8.** Schematic energy-band diagrams of heterojunction diode under zero bias with (a) negative gate voltage, (b) zero gate voltage and (c) positive gate voltage, under forward bias with (d) negative gate voltage, (e) zero gate voltage and (f) positive gate voltage and under reverse bias with (g) negative gate voltage, (h) zero gate voltage and (i) positive gate voltage.

Change of the energy-band diagrams of n-InGaAs–BP heterojunction diode depending on the bias and gate voltages is shown in Figure S8. Here, the electrostatic inversion of BP nanosheets from p-type to n-type as the gate voltage change from negative to positive induces the modulation of the Fermi level of BP, whereas the Fermi level of n-InGaAs remains stationary due to the Fermi-level pinning effect. These behaviors induce the change of the band structure and electrical transport in the heterojunction diode (Figures S8a–c). Here, the band bending of BP at the interface occurs due to the weak Fermi-level pinning which is caused by the defect

and vacancy of molecules in the surface.<sup>2</sup> Due to the modulation of the band structure, the current flow of the heterojunction diode depends on the gate and applied bias voltages. Especially, under the forward bias, the current of device increases at the positive gate voltage due to the decreased barrier height. On the other hand, the flow of holes from BP to InGaAs is dominantly blocked by the barrier at the negative gate voltage, resulting in low current levels as shown in Figures S8d–f. While under reverse bias, the change of current in the device is much smaller than under forward bias because the current flow is blocked by the barrier at positive gate voltage and depends on minority carriers at the negative gate voltage (Figures S8g–i).

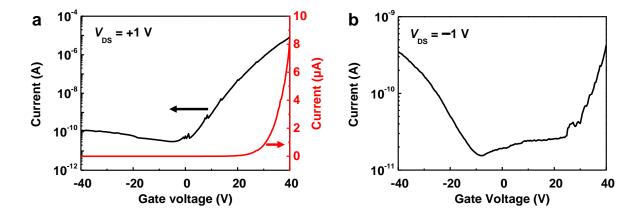

**Figure S9.** a) Transfer characteristics of n-InGaAs–BP heterojunction diode at  $V_{DS} = 1$  V on a linear scale (red) and on a semi-logarithmic scale (black). b) Transfer characteristics of n-InGaAs–BP heterojunction diode at  $V_{DS} = -1$  V on a semi-logarithmic scale.

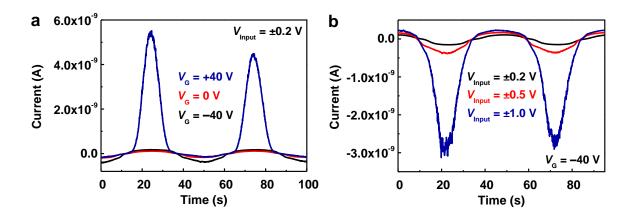

**Figure S10.** (a) Output current of heterojunction diode with sinusoidal input drain-source voltage ( $V_{Input} = -0.2$  to +0.2 V) and under applied gate voltages of -40, 0, 40 V. (b) Output current of heterojunction diode under applied gate voltage of -40 V and with sinusoidal input drain-source voltages of various magnitudes ( $V_{Input} = -1$  to +1, -0.5 to +0.5, and -0.2 to +0.2 V).

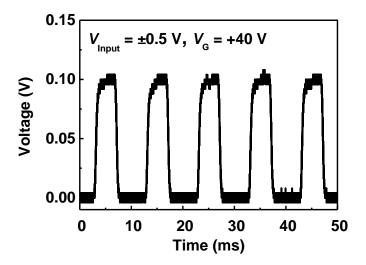

**Figure S11.** Output voltage of n-InGaAs–BP heterojunction diode with external resistor (R =  $1 \text{ M}\Omega$ ) under applied gate voltage of 40 V and sinusoidal input drain-source voltage ( $V_{\text{Input}} = -0.5 \text{ to } 0.5 \text{ V}$ ; 0.1 kHz).

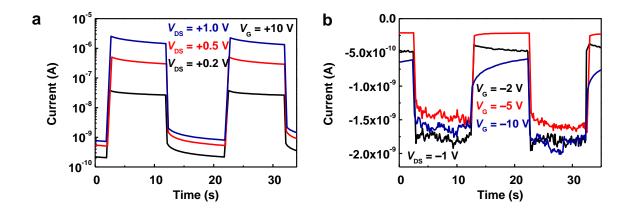

**Figure S12.** (a) Output current of heterojunction diode with rectangular voltage pulse applied to gate ( $V_G = 10 \text{ V}$ ) under forward biases of 0.2, 0.5, and 1 V. (b) Output current of heterojunction diode under reverse bias of -1 V and with rectangular voltage waveform of various magnitudes applied to gate ( $V_G = 2$ , 5, and 10 V).

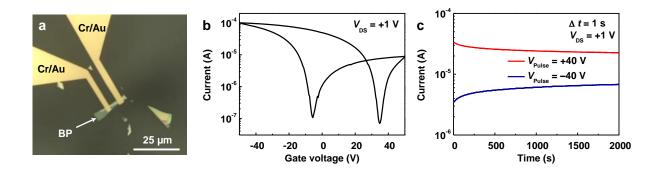

**Figure S13.** (a) Optical-microscope image of BP FET. (b) Transfer characteristics of BP FET under forward bias of 1 V with gate voltage sweep from −50 V to 50 V in positive direction and 50 V to −50 V in negative direction. (c) Retention test of BP FET under forward bias of 1 V with ±40 V applied gate voltage pulses for 1s.

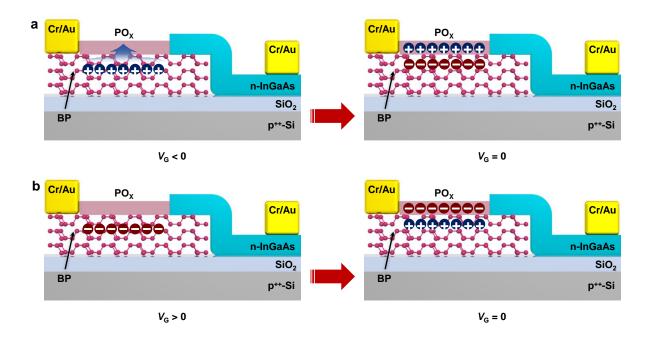

**Figure S14.** Schematics of programmable heterojunction diode in (a) programmed state and (b) erased state.

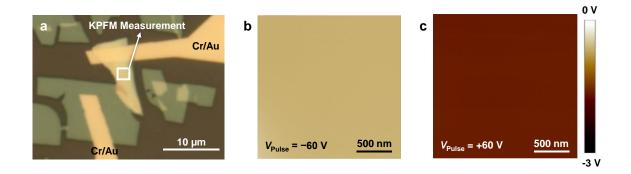

**Figure S15.** (a) Optical-microscope image of n-InGaAs–BP heterojunction diode used for Kelvin probe force scope measurement (KPFM). (b) KPFM image on BP with  $V_{\rm CPD} \sim -0.59~{\rm V}$  after the device is programmed by  $-60~{\rm V}$  applied gate voltage pulses for 1s. (c) KPFM image of BP with  $V_{\rm CPD} \sim -1.65~{\rm V}$  after device is erased by 60 V applied gate voltage pulses for 1s.

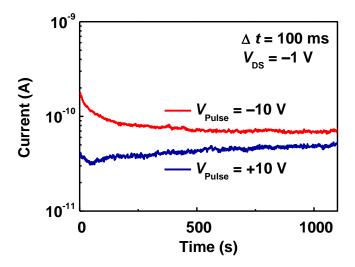

**Figure S16.** Retention test of n-InGaAs–BP heterojunction diode under reverse bias of -1 V with  $\pm 10$  V applied gate voltage pulses for 100 ms.

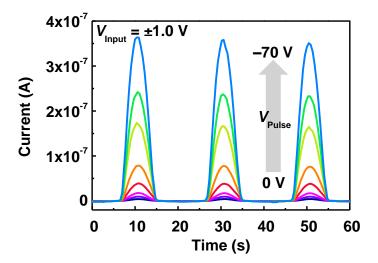

**Figure S17.** Output current of n-InGaAs–BP heterojunction diode with sinusoidal input drain-source voltage ( $V_{\text{Input}} = -1 \text{ to } +1 \text{ V}$ ) and 10 s gate voltage pules ranging from 0 to -70 V.

**Figure S18.** Schematic of energy-band diagram of heterojunction diode under forward bias and zero gate voltage.

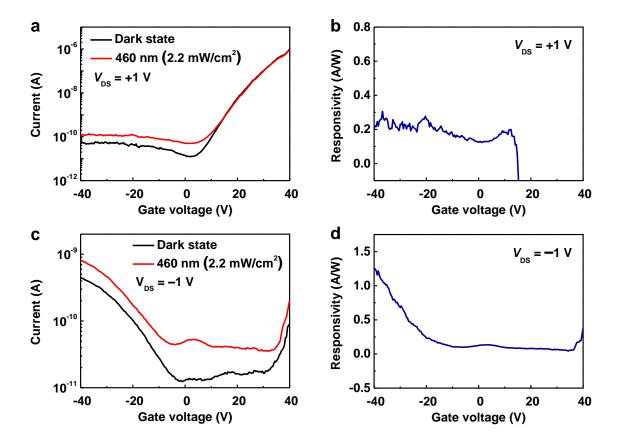

**Figure S19.** (a) Transfer characteristics of n-InGaAs–BP heterojunction diode under forward bias of 1 V in dark and 460 nm light illumination. (b) Responsivity of n-InGaAs–BP heterojunction diode under forward bias of 1 V as a function of gate voltage. (c) Transfer characteristics of n-InGaAs–BP heterojunction diode under reverse bias of −1 V in dark and 460 nm light illumination. (d) Responsivity of n-InGaAs–BP heterojunction diode under reverse bias of −1 V as a function of gate voltage.

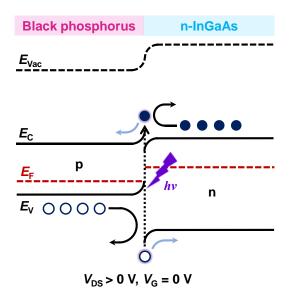

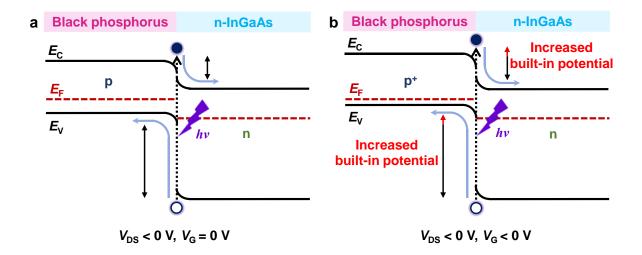

**Figure S20.** Schematic illustration of energy-band diagrams of heterojunction diode under reverse bias with light illumination under (a) zero gate voltage and (b) negative gate voltage states.

Table S1. Comparison of possible functionalities of various multi-functional devices.

| Structure                                                      | Diode                               | Transistor                                                                                       | Memory                               | Photodetector                           | Logic<br>system      | Ref.         |

|----------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------|----------------------|--------------|

| BP/InGaAs<br>heterojunction                                    | R <sub>rec</sub> : 4600             | $M: 84.6 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1};$<br>On/Off ratio: $\sim 10^5$               | <i>T</i> <sub>r</sub> : 1000 s       | R <sub>ph</sub> : 0.704<br>A/W          | ADDER                | This<br>work |

| Si/SWNT<br>heterojunction                                      | _                                   | On/Off ratio: ~10 <sup>5</sup>                                                                   | _                                    | $R_{\rm ph}$ : ~1 A/W                   | AND;<br>OR;<br>ADDER | 3            |

| BP-MoS <sub>2</sub> heterostructure                            | $R_{\rm rec}$ : ~4 ×10 <sup>5</sup> | On/Off ratio: ~10 <sup>7</sup>                                                                   | _                                    | _                                       | Inverter             | 4            |

| MoS <sub>2</sub> -MoTe <sub>2</sub><br>heterostructure         | $R_{\rm rec}$ : $\sim 10^7$         | On/Off ratio: ~10 <sup>8</sup>                                                                   | $R_{\rm pr}$ : ~10 <sup>9</sup>      | R <sub>ph</sub> : ~28.6<br>A/W          | _                    | 5            |

| Graphene-<br>MoS <sub>2</sub><br>heterostructure               | _                                   | $M: \sim 10^4 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$                                        | $T_{\rm r}$ : ~4 × 10 <sup>4</sup> s | $R_{\rm ph}$ : ~5 × 10 <sup>8</sup> A/W | _                    | 6            |

| Multilayer<br>/Monolayer<br>MoS <sub>2</sub><br>heterojunction | $R_{\rm rec}$ : $\sim 10^3$         | M: 0.1-10<br>cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ;<br>On/Off ratio: ~10 <sup>7</sup> | _                                    | $R_{\rm ph}$ : ~10 <sup>3</sup> A/W     | _                    | 7            |

| Layer-<br>controlled BP<br>heterojunction                      | _                                   | $M: 100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1};$<br>On/Off ratio: ~10 <sup>6</sup>           | _                                    | R <sub>ph</sub> : 383 A/W               | _                    | 8            |

$\overline{R_{\text{rec}}}$ : Rectifying ratio, M: Mobility,  $T_r$ : Retention time,  $R_{\text{ph}}$ : Photo-responsivity,  $R_{\text{pr}}$ : Program/erase ratio

## REFERENCES

- (1) Yang, Z.; Liao, L.; Gong, F.; Wang, F.; Wang, Z.; Liu, X.; Xiao, X.; Hu, W.; He, J.; Duan, X. WSe<sub>2</sub>/GeSe Heterojunction Photodiode with Giant Gate Tunability. *Nano Energy* **2018**, *49*, 103-108.

- (2) Kim, C.; Moon, I.; Lee, D.; Choi, M. S.; Ahmed, F.; Nam, S.; Cho, Y.; Shin, H. J.; Park, S.; Yoo, W. J. Fermi Level Pinning at Electrical Metal Contacts of Monolayer Molybdenum Dichalcogenides. ACS nano 2017, 11, 1588-1596.

- Kim, Y. L.; Jung, H. Y.; Park, S.; Li, B.; Liu, F.; Hao, J.; Kwon, Y.-K.; Jung, Y. J.; Kar,

S. Voltage-Switchable Photocurrents in Single-Walled Carbon Nanotube-Silicon

Junctions for Analog and Digital Optoelectronics. *Nat. Photonics* 2014, 8, 239-243.

- (4) Huang, M.; Li, S.; Zhang, Z.; Xiong, X.; Li, X.; Wu, Y. Multifunctional High-Performance van der Waals Heterostructures. *Nat. Nanotechnol.* **2017**, *12*, 1148-1154.

- (5) Cheng, R.; Wang, F.; Yin, L.; Wang, Z.; Wen, Y.; Shifa, T. A.; He, J. High-Performance, Multifunctional Devices Based on Asymmetric van der Waals Heterostructures. *Nat. Electron.* **2018**, *1*, 356-361.

- (6) Roy, K.; Padmanabhan, M.; Goswami, S.; Sai, T. P.; Ramalingam, G.; Raghavan, S.; Ghosh, A. Graphene-MoS<sub>2</sub> Hybrid Structures for Multifunctional Photoresponsive Memory Devices. *Nat. Nanotechnol.* **2013**, *8*, 826-830.

- (7) Sun, M.; Xie, D.; Sun, Y.; Li, W.; Teng, C.; Xu, J. Lateral Multilayer/Monolayer MoS<sub>2</sub>

Heterojunction for High Performance Photodetector Applications. *Sci. Rep.* **2017**, *7*, 4505.

- (8) Wang, L.; Huang, L.; Tan, W. C.; Feng, X.; Chen, L.; Ang, K.-W. Tunable Black Phosphorus Heterojunction Transistors for Multifunctional Optoelectronics. *Nanoscale* 2018, 10, 14359-14367.