# **Supporting Information**

# Electrical-driven Plasmon Source on Silicon based on Quantum Tunneling

Hasan Göktaş<sup>1,2</sup>, Fikri Serdar Gökhan<sup>3</sup>, Volker J. Sorger<sup>1\*</sup> <sup>1</sup>Department of Electrical and Computer Engineering, The George Washington University, Washington, D.C. 20052, USA <sup>2</sup>Department of Electrical and Electronic Engineering, Harran University, Sanliurfa, 63000, Turkey <sup>3</sup>Department of Electrical and Electronic Engineering, Alanya Alaaddin Keykubat University, Kestel, Alanya, Antalya, Turkey

\*Email: sorger@gwu.edu

## 1. Fowler-Nordheim tunneling of MIS (Metal-Insulator-Silicon) Tunnel Junction

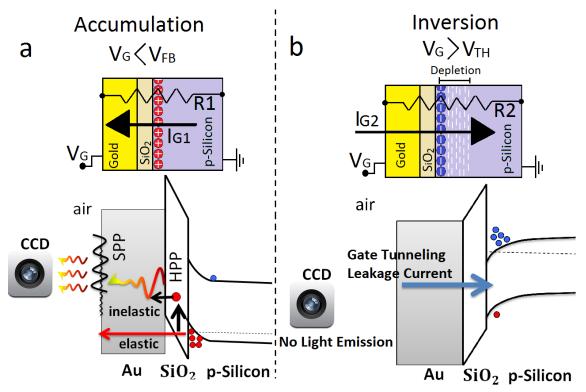

Figure S1. Energy diagram of p-type Si/SiO<sub>2</sub>/Au tunnel junction **a**, when  $V_{bias} < 0$  (Accumulation Region), **b**, when  $V_{bias} > 0$  (Inversion Region)

The plasmon source from the main text relies on currents originating from a quantum tunnel events. The electrical and optical (plasmonic) interplay between current, voltage, and optical mode governs the performance of this device. The core is a metal-insulator-semiconductor structure based on a p-type Silicon-on-insulator substrate. While in a DC capacitor only charge-loading currents can low, here a thin oxide layer facilitates tunnel currents of holes from the semiconductor into the metal in accumulation (Fig. S1a). The current flow in accumulation consists of elastic and inelastic

tunneling ( $\sim 7x10^{-3}$  A). On the other hand, the resistance between metal and silicon is rather high when in inversion, where only gate tunneling leakage current is occurs (around  $1 \times 10^{-12}$  A, Fig. S1b). Hence we can treat this tunnel source as an NMOS transistor and allow the creation of n-type channel between drain and source. The tunnel current density responsible from the plasmon emission is given in [1] and is proportional to the electric field in the oxide layer;

$$I \alpha E_i^2 \exp\left[-\frac{4\sqrt{2m^*}(q\phi_B)^{3/2}}{3q\hbar E_i}\right]$$

(1)

where  $E_i$  is the electric field in the oxide region,  $m^*$  is an effective mas,  $\hat{n}$  is plank constant, and  $\phi_B$  is barrier height. The electric field in the insulator region is proportional to the surface potential and given in [2] as;

$$E_{ox} = \left(V_{bias} + \phi_{Bs} - \phi_{Bm} + \frac{k_B T}{e} ln \left(\frac{N_C}{N_D}\right) - \psi_s\right) / t_{ox} \quad (2)$$

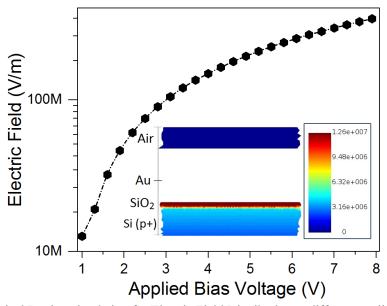

where  $V_{bias}$  is the applied bias voltage,  $\phi_{Bs}$  is the difference between the electron affinities of Si and SiO<sub>2</sub>,  $\phi_{Bm}$  is the difference between the electron affinity of  $SiO_2$  and the work function of the metal,  $t_{ox}$  is the oxide thickness and  $\psi_s$  is the surface potential. Both an increase in the tunneling current (1) or an increase in the applied bias voltage (2) result in a higher electric field in the insulator region (Fig. S2). Up to certain point, the tunneling current is ignorable and very small, however it shows a threshold effect in the IV curve when the electric field is high. This is accompanied by an increase in the light emission intensity.

**Figure S2.** Lumerical Device Simulation for Electric Field Distribution at different applied bias voltage on a p-type Si  $(2\mu m)$  / SiO<sub>2</sub> (2.5 nm) /Au (20 nm) tunnel junction

In contrast to the case given in Fig. S1, it is possible to obtain light emission in both bias polarities (accumulation and inversion). It was achieved by simply introducing n+ doping to the p-Silicon. However, the magnitude of light emission is higher in inversion-compared accumulation although the magnitude of tunneling current in accumulation is higher [2]. This can be attributed to higher electric field at inversion, which results in a higher tunneling rate comprised of hot-electrons, thus feeding the surface plasmon polariton (SPP) mode and the top metal-air interface of the device, resulting in a higher observed light emission.

# 2. Numerical Simulation of Light Emitting Metal-Insulator-Silicon Tunnel Junctions

Two different numerical programs (Lumerical FDTD and Wavenology FDTD) were used to simulate the MIS structure in this work. In one case, bias voltage was used to create the emission and in the other case, dipoles were located in oxide layer to imitate the emission.

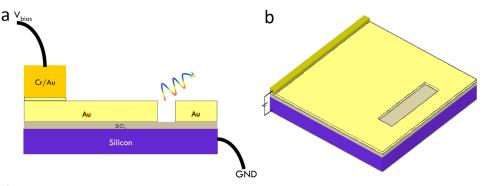

For the model built in Wavenology FDTD: Silicon substrate, SiO<sub>2</sub> and Au films are taken to be 2  $\mu$  m, 2 nm and 100 nm thick, respectively. The dispersive permittivity of Si and SiO<sub>2</sub> are taken from [3], whereas complex permittivity of Au is taken from [4]. As shown in Fig. S3, a 250 nm x 1  $\mu$  m region is assumed to be etched 1.5  $\mu$  m far from the plate where voltage is applied. In order to prevent any plasmonic effects, which might come from the plate, the plate itself is assumed to be a perfect-electrical conductor (PEC). Another very thin PEC film placed under the Si substrate and a DC voltage is applied between these two PEC spots. Wavenology solves for circuit and Maxwell' s equations simultaneously on the same grid using finite-difference time-domain (FDTD) method. To guarantee high numerical accuracy, a 30 points-per-wavelength sampling density is utilized over the whole simulation domain. In order to take doping level into account, the conductivity of Si is set to  $\sigma = q(\mu_n n + \mu_p p)$ , where  $\mu_n$  and  $\mu_p$  are the mobility of electrons and holes, respectively; where n and p are their doping levels.

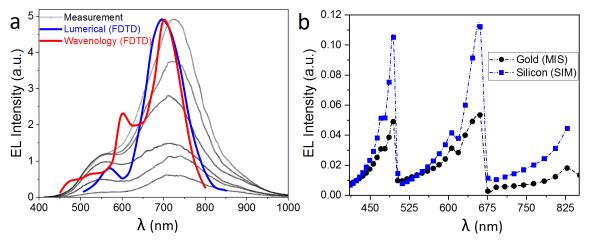

For the model built in Lumerical FDTD: Dipoles are located in oxide layer to imitate the light emission while a surface roughness on 20nm thick Gold (index from Palik) layer is created in MIS structure. A high mesh FDTD (8/8) with a stability factor of 0.95 was applied. An extra high mesh box was added to get further improvement in accuracy. Both Lumerical FDTD and Wavenology FDTD show a double-peak spectrum that match the measurement centered around 720 nm and 550 nm (Fig. S4a). The overall shape is not simply given by the quantum condition  $E = hv = qV_{bias}$ , but depends on the convolution of the spectrally dispersive tunnel current density with that of the eigenmode of the system, namely the hybrid photon plasmon mode [5]. The spectral power density depends on current-fluctuations leading to plasmon creation; small fluctuations in the tunnel current lead to electric field fluctuations, which in turn accelerate and decelerated electrical carriers acting as a plasmon source. As such the spectral dispersion of the internal hybrid plasmon mode is material sensitive [5]. Following this line of thought, our modeling confirms the experimentally observed spectral double peak with exponential decaying emission intensity (Fig. S4a) [5, 6].

Figure S3. a, Two-dimensional and b, three-dimensional view of the simulated structure in Wavenology

**Figure S4. a,** The junction's spectrum is centered around 720 nm increases with bias in steps of one Volt. Lumerical FDTD simulation result for 20 nm thick Gold (with surface roughness), when dipoles are used as a light emission source and Wavenology FDTD results for 20nm thick Gold when Voltage source is applied to create emission. **b,** Emission performance comparison between MIS and SIM structures in Lumerical FDTD

Further studies were conducted via building the SIM (Silicon-insulator-metal) to compare its emission performance with MIS (metal-insulator-silicon) (Fig. S4b). Results show a higher emission intensity for the SIM structure simply because of the lower absorption of the semiconductor than the metal.

#### 3. Grating Design, Experimental Test, and Analysis

Technologically a higher light output is desired for a light source. Since the top metal blocks the emission normal to the sample via absorption, flipping the metal insulator semiconductor (MIS) tunnel junction up-side-down to an SIM configuration (i.e. metal at bottom, and semiconductor on top) renders the use of established silicon-on-insulator (SOI) platforms unusable. Hence our design and approach is based on an SOI MIS configuration. Here, light emission is still limited by the top metal, which can be reduced, however by thinning the top metal. A second option to obtain higher light output is trivial and would be to increase the bias voltage. However thermal non-linearity leads to instabilities of the device, whereas the electric field breakdown voltage sets a fundamental upper voltage limit. Optically, the device operation involves three optical modes, which we discuss next from the inside out; (i) a hybrid plasmon polariton mode inside the MIS tunnel junction termed HPP mode, (ii) a SPP mode at the top of the metal-air interface, and (iii) free space photons leaving the device and being captured by the naked eye/detector/camera. In operation both the HPP- and SPP modes are intrinsically nonradiative. Increasing the overall outcoupling efficiency requires a facilitating improved coupling between all three involved modes [7] via wavevector matching, which can be achieved either by dispersion engineering, or via a grating structure [8]. There are a variety of parameters effecting the MIS diode's light emission intensity  $(I_e)$  with respect to grating parameters  $(\Lambda, d, \theta, \text{ and } \epsilon)$  [5, 7-14];

$$I_e \approx \frac{P(k,w)}{exp\left(\frac{\lambda_e}{L_x}\right)} \quad where \ L_x = \frac{1}{2k_i}, k = Ksin\theta \pm nG, \ G = \frac{2\pi}{\Lambda}, \ k, k_i \sim \frac{\epsilon}{t_{ox}}$$

(1)

where is the corresponding wavelength, k is the momentum,  $n = 1, 2, 3..., \theta$  is the emission angle,  $\lambda_e$  is the effective wavelength,  $\Lambda$  is the grating period,  $t_{ox}$  and  $\epsilon$  are the thickness and dielectric constant of oxide layer respectively. Increase in the light emission intensity  $(I_e)$  with respect to

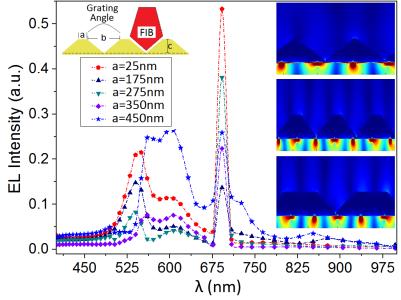

increase in  $\theta$  and  $\epsilon$  or decrease in  $t_{ox}$  and  $\Lambda$  are expected due to increase in k and decrease in  $L_x$  (1) as demonstrated in [9] and [5]. Furthermore, coupling the HPP mode efficiently into the light requires  $\Lambda \sim \lambda_e$  where  $\lambda_e < 80 \text{ nm}$  (3 eV) [5]. However, the gratings duty cycle also affects the light emission efficiency (Fig. S5). We investigated the grating impact via a grating shape-dependent analysis. Here we assumed the metal thickness optimized (20 nm) case; the grating angle was kept constant as it only depends on the beam diameter of the focused-ion-beam (FIB) in the fabrication process, while the duty cycle was changed to create different grating shapes. The advantage of this approach (changing duty cycle) is basically to eliminate the necessity of using tiny grating period ( $\Lambda \sim \lambda_e$  where  $\lambda_e < 80 \text{ nm}$  (3 eV) [5]), which may be challenging for during FIB ion milling, which could also lead to challenges in production yield for actual technology. The Lumerical simulation results with different duty cycle and its spectrum (Fig. S5) suggests that there is an optimum duty cycle (a = 25 nm) with respect to obtaining maximum light emission intensity.

**Figure S5.** The spectrum and light emission profile for different duty cycle derived by Lumerical simulation, where a represents duty cycle and c represents the grating thickness.

#### 4. Emission Efficiency and Relative Efficiency

The external, or wall-plug, quantum efficiency ( wallplug) of the light emitting tunnel junction's emission is given by the product of two factors; namely the internal light (here plasmon) creation ( int) times an outcoupling efficiency factor, simply via:

$$\eta_{wallplug} = \eta_{int} \cdot \eta_{outcouple}$$

(1)

Our procedure to obtain a numerical value for Eqn (1) is as follows; (i) we measure the captured optical power from the emitting device using a CCD camera by integrating over the number of pixels times their grey-scale level, thus obtaining a single scalar representative of the optical power captured by the camera. (ii) Calibrate the optical power captured by an LED with similar spectral response to the tunnel junction, and again obtain an integrated scalar. (iii) Dividing the two values from (i) and (ii), we obtain a value for wallplug, which we found to be  $4.8(\pm 3.5) \times 10^{-4}$ . We note, however, that this value varies depending on the history on the sample, applied bias, and device

junction size. For instance, we find that the conversion efficiency initially increases with bias to about 4-5V, and then sharply drops. In addition, we find that smaller junctions show higher conversion efficiency than large ones (details reported elsewhere). Both effects suggest resistive, and likely thermo-resistive effects inside the junction where high device temperatures increase the resistance due to joule heating.

All devices were operated a room temperature and non-thermo-stabilized to probe the intrinsic behavior of the devices. To control performance, actual devices should be thermally stabilized, and/or cooled. The decline in the conversion efficiency with bias is also evident as each device could be driven to failure where metal oxidation occurred, accompanied by oxide break-down, and a dramatic reduction in photon emission (low conversion despite a near-shorted device). This effect is observed in Fig. 3e of the main text. In addition, cycling this light source for actual large-signal modulation (see supplementary video) stresses the oxide by introducing defect states. This lowers the effective oxide over time and reduces the conversion efficiency.

In order to gain further insights into the two components on the right-hand-side of (1), we performance numerical simulations to estimate the outcoupling efficiency to free space facilitated by the grating. The numerical simulations (Fig. 3f main text) suggest an outcoupling enhancement factor of about 4-fold. To confirm this, we treat this as an antenna problem by taking the ratio of an estimated source impedance ( $R_{radiation}$ ) of the plasmon MIS mode without grating and the free-space impedance ( $z_0 = 377\Omega$ ). Thus, averaging the effect of the grating (8x + 3x)/2 ~ 5x improvement which matches our observed 4x well. The effective wavelength ( $\lambda_{MIS}$ ) in Eqn (2) depends on which method is used to determine the optical modal area [15]. The parameter *a* is the physical length of the radiating antenna, and here approximated by a radiating dipole equivalent to the size of the effective mode wavelength.

$$R_{radiation} = \frac{\omega^2}{6\pi\varepsilon_0 c^3} \cdot a^2 = \sqrt{\frac{\mu_0}{\varepsilon_0}} \frac{2\pi}{3} \left(\frac{a}{\lambda}\right)^2$$

with

$$a \propto \lambda_{MIS} \approx \lambda_0 \cdot \left[\frac{1}{4}, \frac{1}{3}\right] \quad and \quad z_0 = \sqrt{\frac{\mu_0}{\varepsilon_0}} = 377\Omega^{(2)}$$

$$\eta_{outcouple} \approx \frac{R_{radiation}}{z_0} = \left[12.5, 33.3\%\right]$$

With results from (2) we can estimate the internal quantum efficiency,  $\eta_{int}$ , to be  $O \sim 10^{-4}$ . Naturally, an engineering aim would be to increase this conversion efficiency. Here, we note that the Purcell effect, which helps to accelerate the downward transition of an excited state and thus facilitates increasing the brightness of an emitter, cannot be used to enhance  $\eta_{int}$ . This is because the temporal response of the tunnel process is on the order of a femtosecond (using Heisenberg's uncertainty principle, and  $\lambda_{\text{emission}} \sim 2\text{eV}$ ).

The outcoupling efficiency is calculated as 5x (2), and derived as 4x via Lumerical FDTD. These two findings are reasonably close to the ratio of 3.1x (between sine shape grating and no-grating) at 8V (Main Manuscript Figure 3e) where the increase in efficiency are maximized and saturated for all three devices. All three devices are very close to failure due to joule heating and relatively high thermal stress (Fig S6). That is why, the outcoupling efficiency can be estimated to be 4x. The

relative efficiency increases up to 40.9x at 5.1 V (Figure 3e main manuscript), where the outcoupling efficiency is assumed to be 4x. That's why the increase in the internal efficiency is derived as 10x (40.9/4=10).

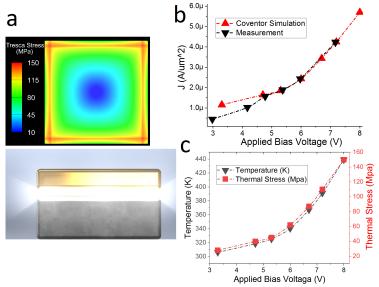

### 5. Device Reliability

Metal (20 nm Au)-insulator (2.5 nm SiO<sub>2</sub>)-Silicon (500 µm) structure was built in Coventor to study the thermal stress. Applying DC bias voltage between top metal and substrate (silicon) results in joule heating and can cause device failure due to high thermal stresses. The electrical conductance is derived from measurement for each applied bias voltage and imported into Coventor simulation. The current density in simulation match our experimental measurements well (Fig. S6). The temperature profile and thermal stress originating from Joule heating were derived from Coventor simulation for each applied bias voltage (Fig. S6c). The temperature on substrate (Silicon) bottom is assumed to be 300 K (Room temperature). A high mesh density was used for more accurate results. The maximum stress was found as 150 MPa when 8 V bias voltage applied on the device. This is close but still below an ultimate strength of any material used in device fabrication. In another words, any small further increase in voltage bias beyond this point may result in device failure [16]. Indeed, most experimental devices biased beyond 8V shorted. On the other hand, the thermal stress at 5.3 V is around 45 MPa, which is well below the ultimate tensile strength of each material in the junction. This demonstrates that the LETJ device in this work should be robust and reliable at 5.3 V. However, between 6-8 Volts we do observe a decline in the electroluminescencevoltage output, which we contribute to excessive heating.

**Figure S6. a,** Thermal stress profile on oxide-metal interface cross section from top view for Au (20 nm) / SiO<sub>2</sub> (2.5 nm) / Si (500  $\mu$ m) at 8V **b**, Current density versus applied bias voltage **c**, Thermal stress and temperature with respect to applied bias voltage

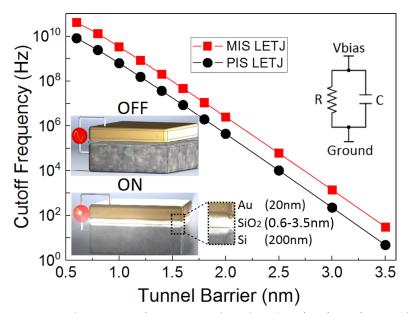

## 6. Cut off Frequency Prediction

Because the emission originates from the rapidly-thermalized Fermi-sea of a semiconductor and into the conduction band of a metal, the limiting processes do not follow the standard rate equations of light emitters and lasers. From Heisenberg's uncertainty principle, large optical bandwidths imply inelastic tunneling speeds on the order of 10's of femtoseconds. Indeed, the temporal response of a tunnel event has been measured as short as 100 atto seconds [17]. Comparing this to recombination lifetimes of direct and indirect bandgap semiconductors such as GaAs and Si, which

are on the order of nanoseconds and milliseconds, respectively, we find that tunnel junctions may allow for a high modulation speed [13, 18]. With the delay of the actual tunnel being negligible, we analyze the electrical circuit-related constrains to understand the junction's actual response time. The limiting factor is related to resistive and capacitive (RC) effects of the junction itself [19]. Our MIS tunnel source is a planar structure acting as a parallel plate capacitor (Fig. S7). Here, the relevant resistance in this case is not the line impedance but the resistance. For inelastic tunneling events to be dominant, the electron tunnel current must dominate the displacement current across the capacitor. Note, that the tunnel resistance scales inversely with area, whereas capacitance scales linearly, yielding an RC time constant invariant to area in an ideal case. However, the tunnel resistance scales exponentially with thickness, while the capacitance scales only linearly. As a result, high modulation speed (>40 GHz) can be achieved with sufficiently thin tunnel oxides (0.6 nm, Fig. S7). The latter is technologically achievable by adjusting the deposition cycle in the atomic-layer-deposition process (Fig. S7) [20, 21]. The equivalent circuit of the MIS diode was derived as parallel RC [22] and the cut off frequency of RC is;

$$f_c = \frac{1}{2\pi RC}$$

,  $\mathbf{R} = \frac{V_{bias}}{JA}$ ,  $\mathbf{C} = \epsilon_0 \epsilon_r \frac{A}{t_{ox}}$

where J is the tunneling current density and was derived using Silvaco where the Silicon thickness is 200 nm for both PIS and MIS device. Replacing the top metal of the MIS junction with a polysilicon drops the speed to  $\sim$ 8 GHz due to lower tunneling current originating from the higher resistance of the doped semiconductor vs. the metal (Fig. S7).

Figure S7. Direct modulation speed of the tunnel junction. Results show that at 10's of GHz-fast modulation are possible for tunnel oxides less than one nanometer ( $V_{bias} = -3.4$ V). MIS = metal-insulator-semiconductor and PIS = polysilicon-insulator-semiconductor. Silicon thickness = 200 nm Inset: plasmon emitting tunnel junction layout and its equivalent circuit model.

It is worth mentioning, that the metal serves a triple function in this light source; (i) metal confines the optical mode enabling device scalability via allowing for sub-diffraction limited modes as we have previously shown for hybrid plasmons [23], (ii) metal is a heat sync, since replacing the top metal with poly Silicon lowers the device temperature enabling higher modulation speeds (i.e.  $P_{dissipated} = E/bit \ge bitrate$ ) [23], and (iii) metal acts as an electrical contact allowing for low-voltage drops in the contacts leading up to the device. The latter is not possible for photonic devices as their optical loss from heavy-doped (low resistance) semiconductors is detrimental to the insertion loss devices [24]. Interestingly, the modulation speed can be accelerated further by increasing the inelastic tunneling probability via the Purcell factor, which could be achieved by introducing nanoscale cavities [25-27]. Such acceleration of emission processes will thus further decrease the tunneling resistance, hence increasing direct modulation speed. This also leads to an enhanced quantum efficiency and thus wall-plug efficiency, in analogy to the spontaneous emission factor reducing the laser threshold [28].

#### References

1. Sze, S. M., & Ng, K. K. Physics of Semiconductor Devices Ch. 4 (John Wiley & Sons, Inc., Publication, New Jersey, 2007).

2. Watanabe, J., Uehara, Y., Murota, J. & Ushioda, S. Light Emission from Si-Metal-Oxide-Semiconductor Tunnel Junctions. *Jpn. J. Appl. Phys.* **32**, 99-104 (1993).

3. E. D. Palik, Editor, Handbook of Optical Constants of Solids, Vol. 1, Academic Press Publishers, (1985).

4. A. D. Rakic, A. B. Djurisic, J. M. Elazar, and M. L. Majewski, "Optical properties of metallic films for vertical-cavity optoelectronic devices," Appl. Opt. 37, 5271–5283, (1998).

5. Szentirmay, Zs. Slow-mode surface plasma oscillations in layered structures. *Phys. Rev. B*. **36**, 2607-2613 (1987).

6. Wang, MX., Yu, JH. & Sun, CX. Light emission characteristics and negative resistance phenomenon of Si-based metal/insulator/semiconductor tunnel junction. *Appl. Surf. Sci.* **161**, 9-13 (2000).

7. Connolly, M. P., Whitaker, M. A. B. & Dawson, P. Calculation of slow mode surface plasmon polariton properties related to experimental observations. *Appl. Phys. Lett.* **61**, 2776-2778 (1992).

8. Ushioda, S., Uehara, Y., Takada, M., Otsubo, K. & Murota, J. Grating-Coupled Light Emission from the Slow Mode of Metal-Insulator-Metal Tunnel Junctions. Jpn. J. Appl. Phys. 31, L870-L873 (1992).

9. Sparks, P. D., Sjodin, T., Reed, B. W. & Stege, J. Light Emission from the Slow Mode of Tunnel Junctions on Short Period Diffraction Gratings. *Phys. Rev. Lett.* **68**, 2668-2671 (1992).

10. Kirtley, J. R., Theis T. N. & Tsang, J. C. Diffraction-grating-enhanced light emission from tunnel junctions. Appl. Phys. Lett. 37, 435-437 (1980).

11. Kirtley, J. Theis, T. N. & Tsang, J. C. Light emission from tunnel junctions on gratings. Phys. Rev. B. 24, 5650-5663 (1981).

12. Kroó, N., Szentirmay, Zs. & Félszerfalvi, J. On the mechanism of photon emission from thin film tunnel structures. Acta Phys. Hung. 51, 177-191 (1981).

13. Ferguson, A. J. L., Walmsley, D. G., Hagan, H. P., Turner, R. J., & Dawson, P. Spectral dependence of light output from LEIT devices on electrode morphology. J. Phys. Condens. Matter 1, 7931-7940 (1989).

14. Goktas H. & Sorger, V. J. Sub-wavelength Si-based plasmonic light emitting tunnel junction. Proc. SPIE 9668, Micro+Nano Materials, Devices and Systems (Sydney, New South Wales, Australia, 2015).

15. Oulton R. F., Bartal G., Pile D. F. P. and Zhang X. Confinement and propagation characteristics of subwavelength plasmonic modes. *New J. Phys.* **10**, 105018 (14pp) (2008).

16. Göktaş, H. & Zaghloul, M. E. The Novel Microhotplate: A Design Featuring Ultra High Temperature, Ultra Low Thermal Stress, Low Power Consumption and Small Response Time. SENSORCOMM (Barcelona, Spain, 2013).

17. Uiberacker, M. et al., Attosecond real-time observation of electron tunneling in atoms, *Nature* **446**, 627-632 (2007).

18. Gramotnev, D. K., Bozhevolnyi, S. I. Plasmonics beyond the diffraction limit. Nat. Phot. 4, 83-91 (2010). 19. Ma Z., Tahersima M. H., Khan S. and Sorger V. J., "Two-Dimensional Material-Based Mode Confinement Engineering in Electro-Optic Modulators," *IEEE Journal of Selected Topics in Quantum Electronics*, **23**, 1, 1-8 (2017).

20. Busch, B. W. Materials Characterization of Alternative Gate Dielectrics. MRS Bulletin 27, 206-211 (2002).

21. Grigora, K. et al. Application of ultra-thin aluminum oxide etch mask made by atomic layer deposition technique. Journal of Physics 61, 369-373 (2007).

22. Yang, K. J. & Hu, C. MOS capacitance measurements for high-leakage thin dielectrics. IEEE Trans. Electron Devices 46, 1500-1501 (1999).

23. Liu, K., Li, N., Sadana, D. K. & Sorger, V. J. Integrated Nanocavity Plasmon Light Sources for On-Chip Optical Interconnects. *ACS Photonics* **3**, 233-242 (2016).

24. Sorger, V. J. *et al.* Roadmap vectors of attoJoule per bit modulators. IOP Journal of Optics **20**, 014012 (16pp) (2018).

25. Sorger, V. J. et al. Strongly Enhanced Molecular Fluorescence inside a Nanoscale Waveguide Gap. Nano Lett. 11, 4907-4911 (2011).

26. Tahersima, M. H. et al. Testbeds for Transition Metal Dichalcogenide Photonics: Efficacy of Light Emission Enhancement in Monomer vs Dimer Nanoscale Antennae. ACS Photonics 4, 1713-1721 (2017).

27. Liu K. & Sorger, V. J. Enhanced interaction strength for a square plasmon resonator embedded in a photonic crystal nanobeam cavity. Journal of Nanophotonics 9, 093790 (2015).

28. Davis, L.C. Theory of surface-plasmon excitation in metal-insulator-metal tunnel junctions, *Physical Review B*, **16**, 2482-2490 (1977).